## Contents

|                                                                       |           |

|-----------------------------------------------------------------------|-----------|

| <b>1 FEATURES .....</b>                                               | <b>5</b>  |

| <b>2 GENERAL DESCRIPTIONS.....</b>                                    | <b>6</b>  |

| <b>3 MEMORY ORGANIZATION.....</b>                                     | <b>10</b> |

| <b>4 DEVICE OPERATIONS.....</b>                                       | <b>11</b> |

| 4.1 SPI MODE .....                                                    | 11        |

| 4.2 QPI MODE.....                                                     | 11        |

| 4.3 RESET FUNCTION .....                                              | 11        |

| 4.4 ENTER XIP MODE DIRECTLY AFTER POWER-ON (POR-XIP).....             | 12        |

| <b>5 DATA PROTECTION.....</b>                                         | <b>13</b> |

| <b>6 REGISTERS.....</b>                                               | <b>19</b> |

| 6.1 STATUS REGISTER .....                                             | 19        |

| 6.2 EXTENDED ADDRESS REGISTER .....                                   | 22        |

| 6.3 FLAG STATUS REGISTER .....                                        | 23        |

| <b>7 INTERNAL CONFIGURATION REGISTER .....</b>                        | <b>25</b> |

| 7.1 NONVOLATILE CONFIGURATION REGISTER .....                          | 25        |

| 7.2 VOLATILE CONFIGURATION REGISTER .....                             | 26        |

| <b>8 COMMAND DESCRIPTIONS.....</b>                                    | <b>28</b> |

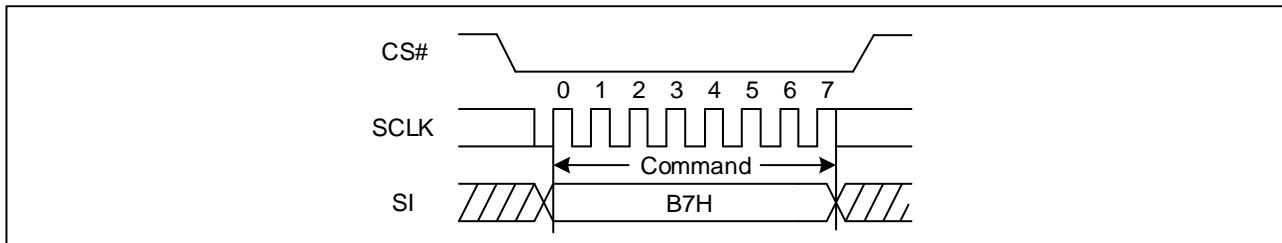

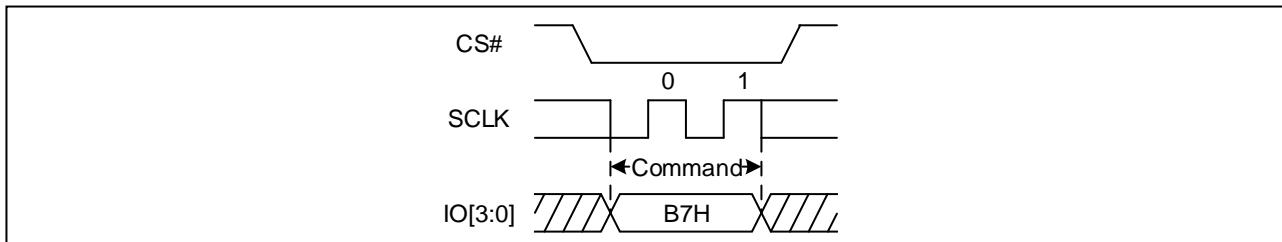

| 8.1 ENABLE 4-BYTE MODE (B7H) .....                                    | 37        |

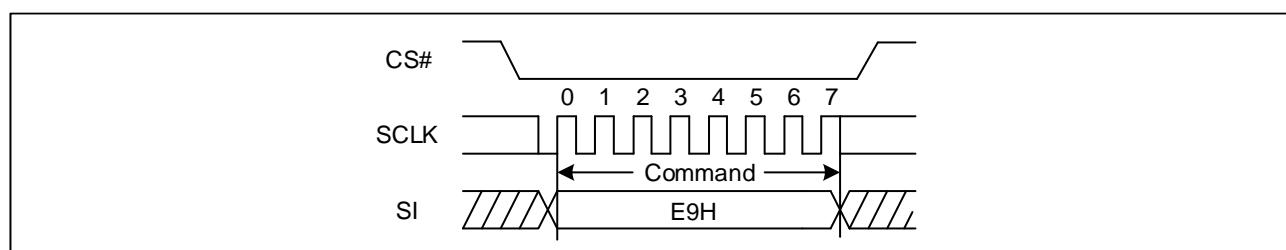

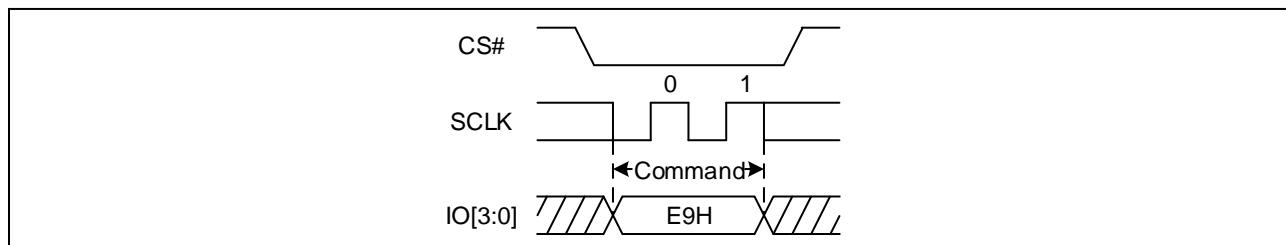

| 8.2 DISABLE 4-BYTE MODE (E9H).....                                    | 37        |

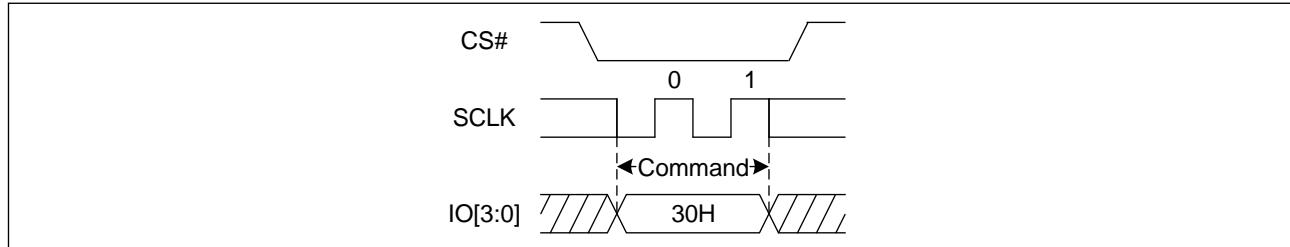

| 8.3 CLEAR FLAG STATUS REGISTER (30H).....                             | 38        |

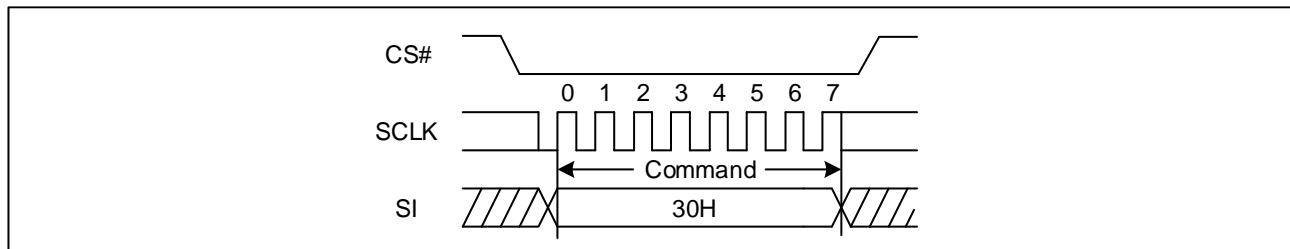

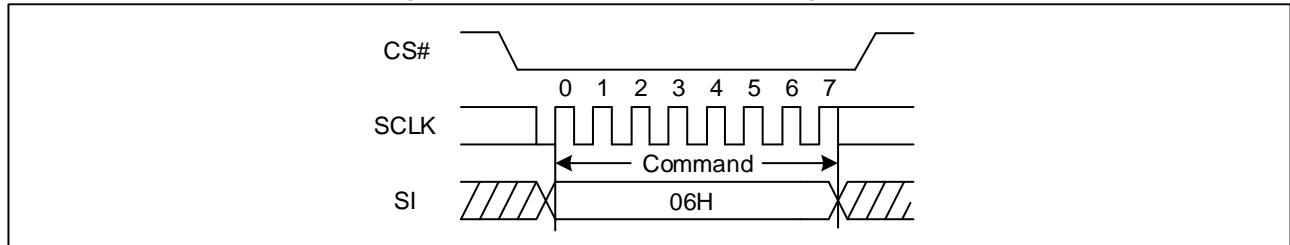

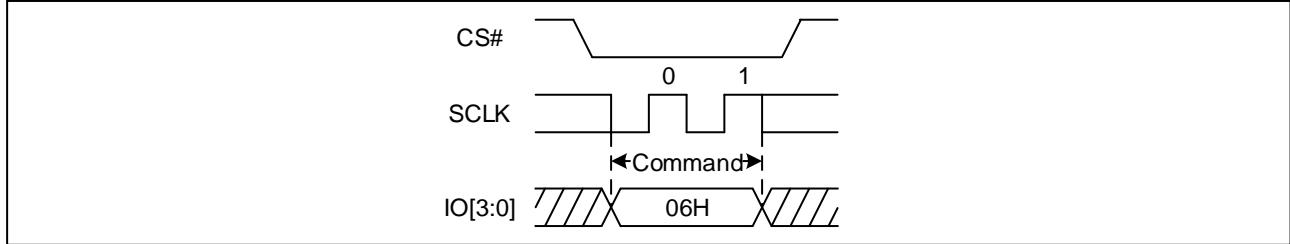

| 8.4 WRITE ENABLE (WREN) (06H).....                                    | 38        |

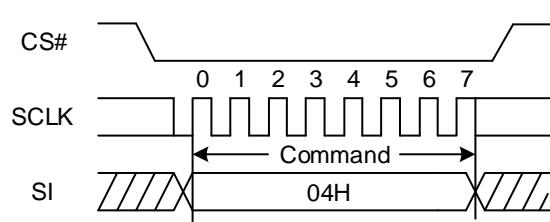

| 8.5 WRITE DISABLE (WRDI) (04H) .....                                  | 39        |

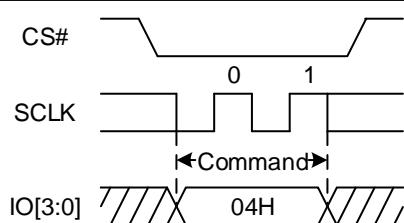

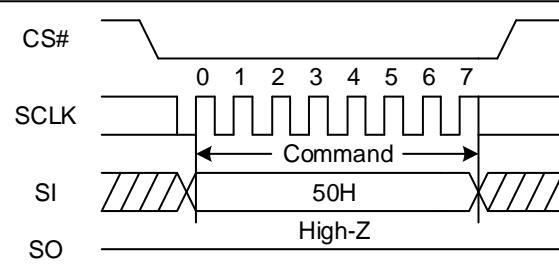

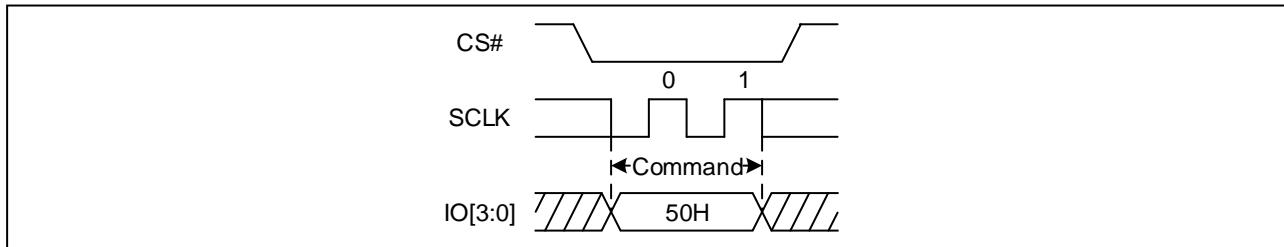

| 8.6 WRITE ENABLE FOR VOLATILE STATUS REGISTER (50H) .....             | 39        |

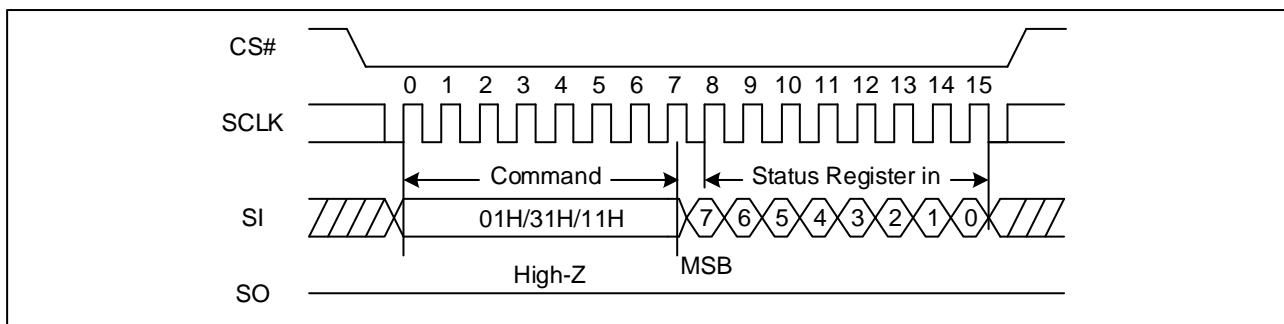

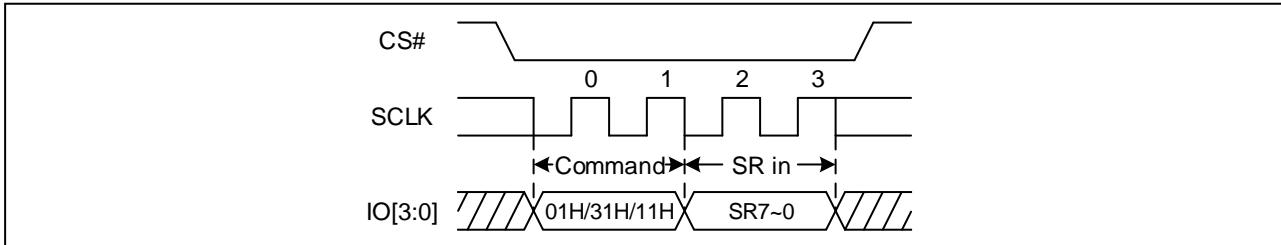

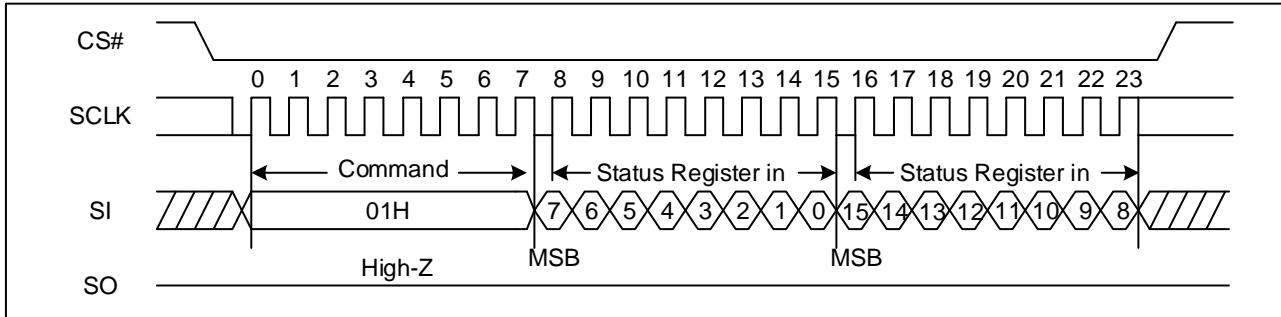

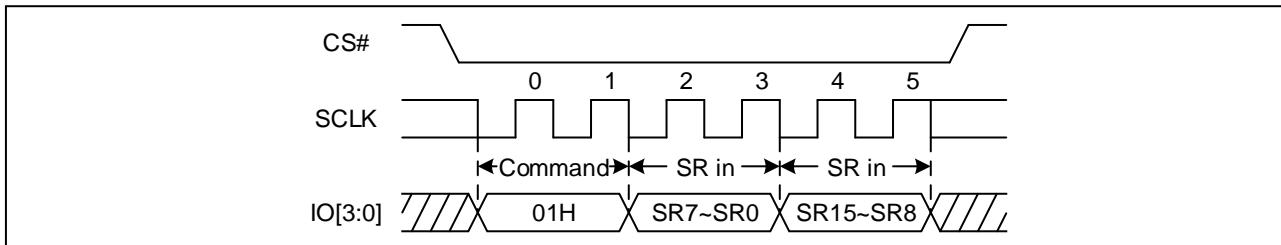

| 8.7 WRITE STATUS REGISTER (WRSR) (01H/31H/11H) .....                  | 40        |

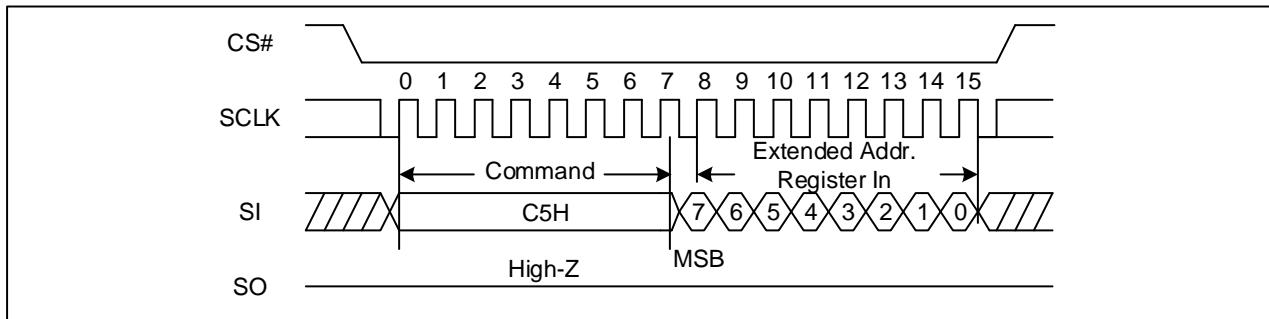

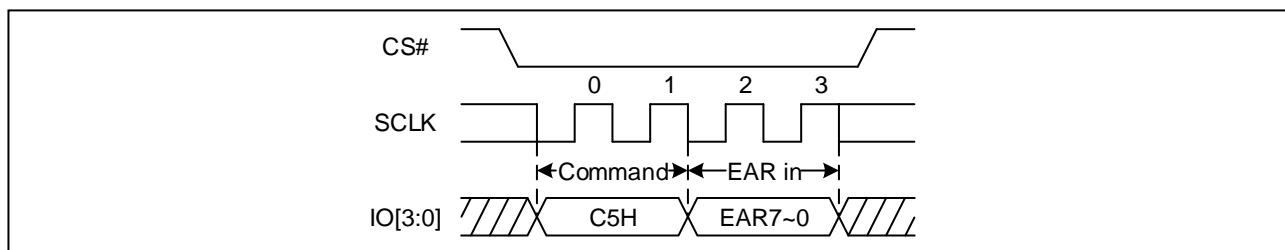

| 8.8 WRITE EXTENDED ADDRESS REGISTER (C5H).....                        | 41        |

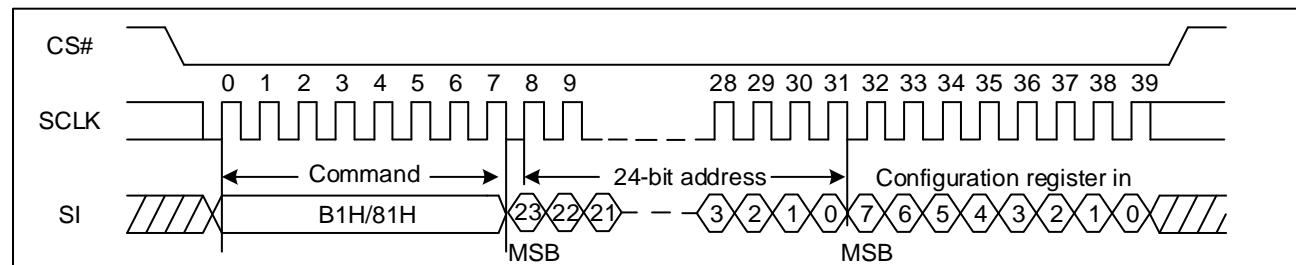

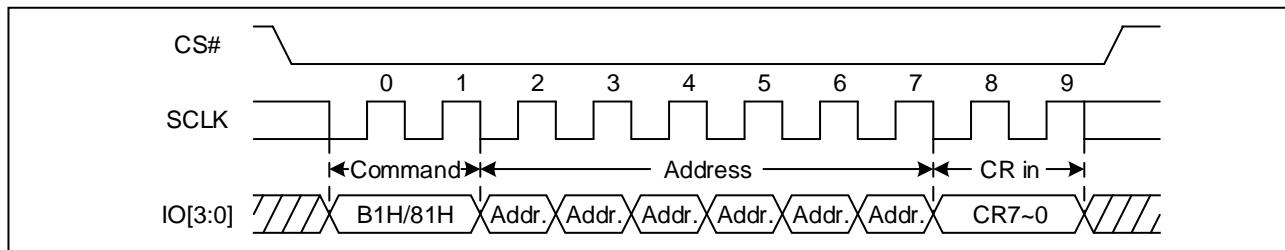

| 8.9 WRITE NONVOLATILE/VOLATILE CONFIGURATION REGISTER (B1H/81H) ..... | 42        |

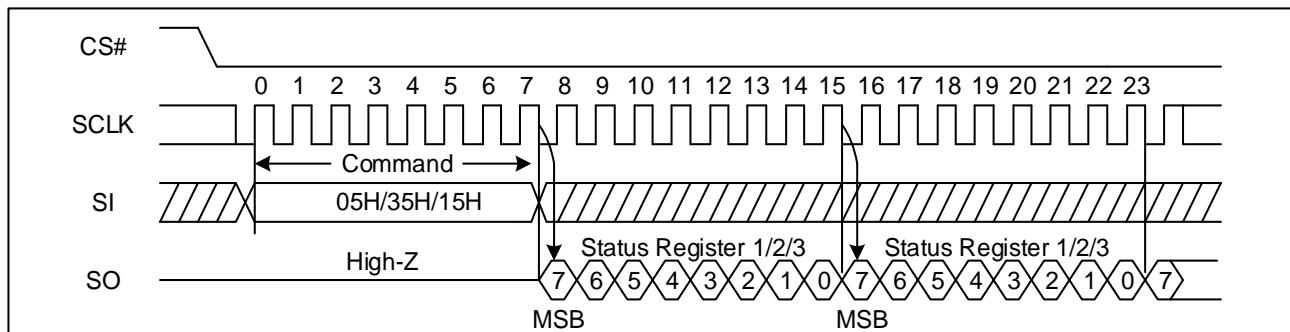

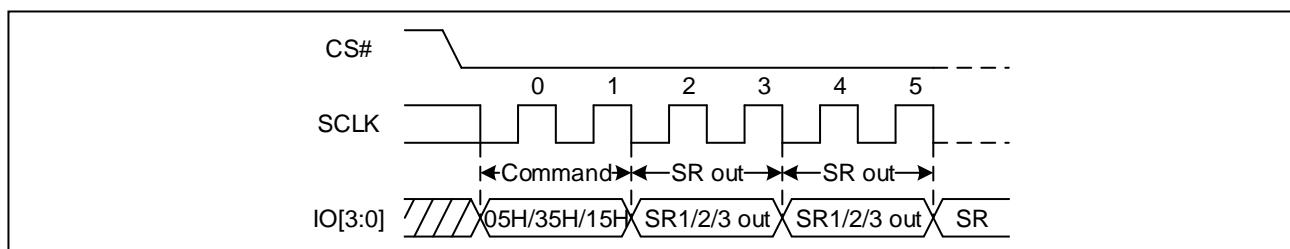

| 8.10 READ STATUS REGISTER (05H/35H/15H) .....                         | 43        |

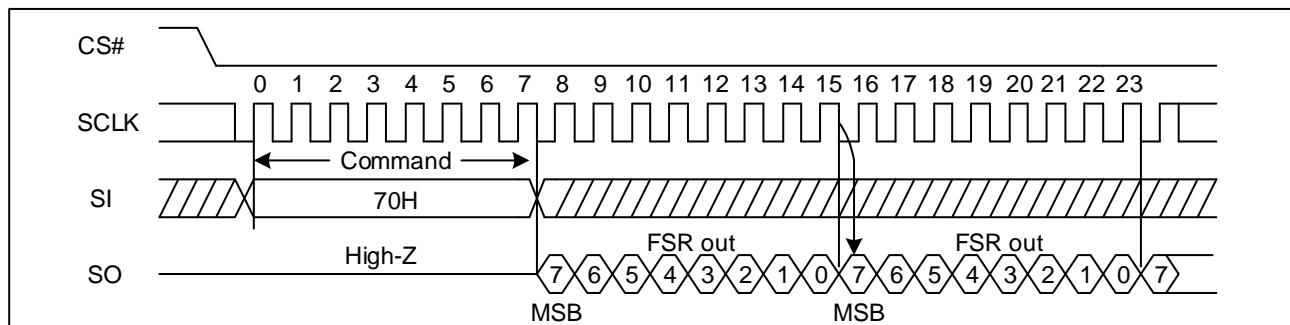

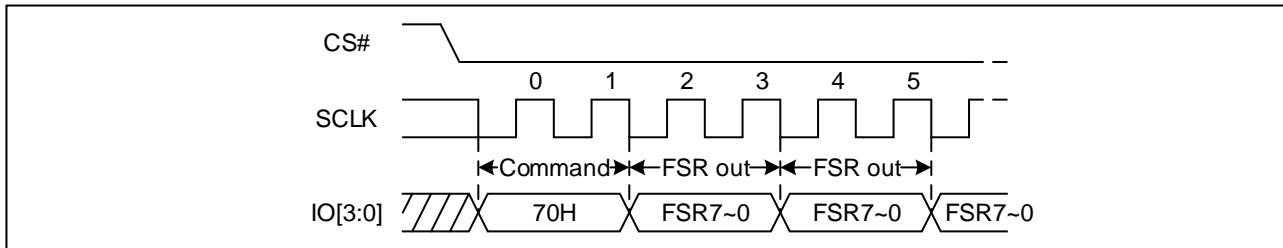

| 8.11 READ FLAG STATUS REGISTER (70H).....                             | 43        |

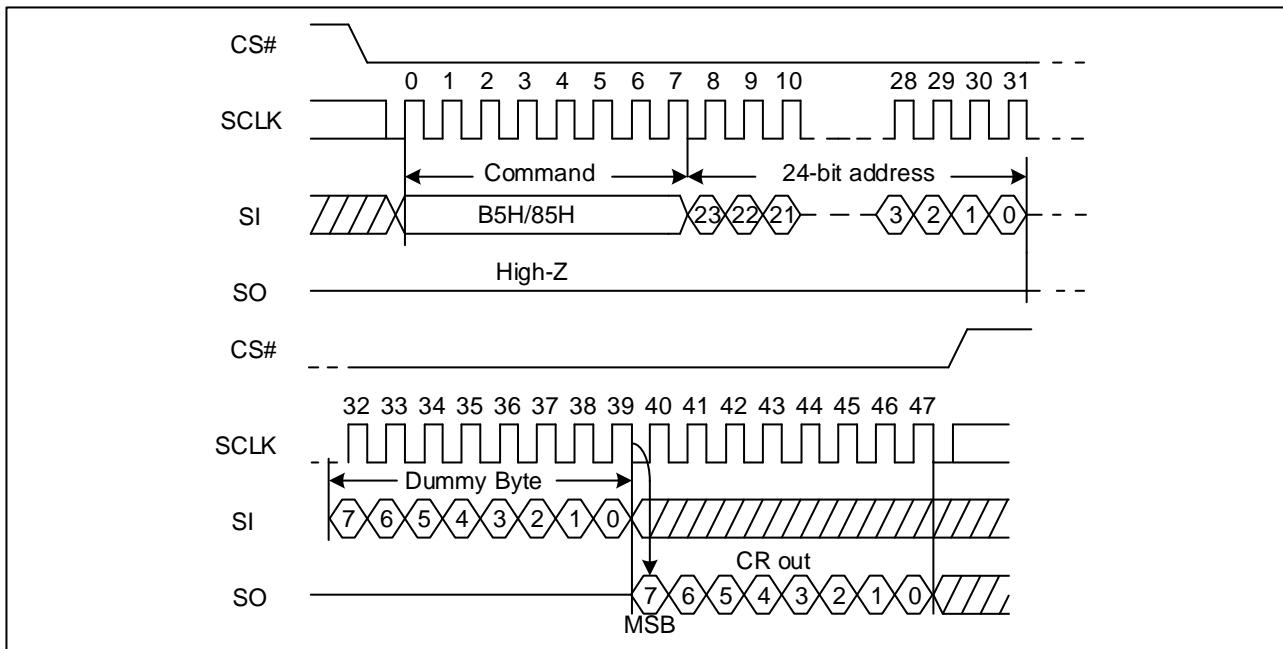

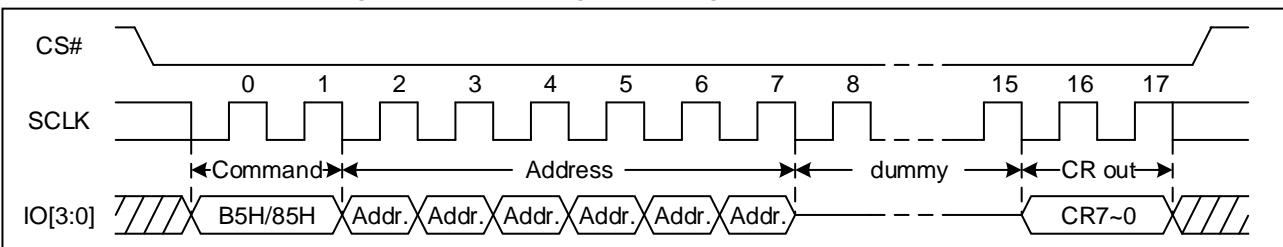

| 8.12 READ NONVOLATILE/VOLATILE CONFIGURATION REGISTER (B5H/85H).....  | 44        |

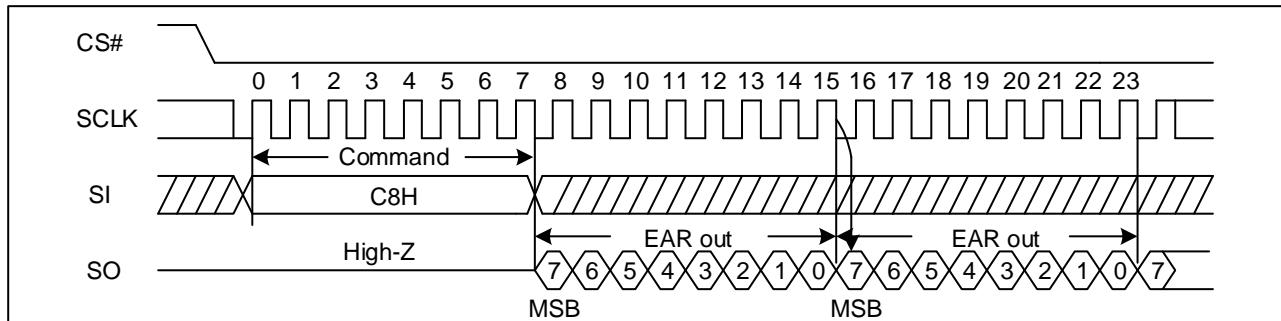

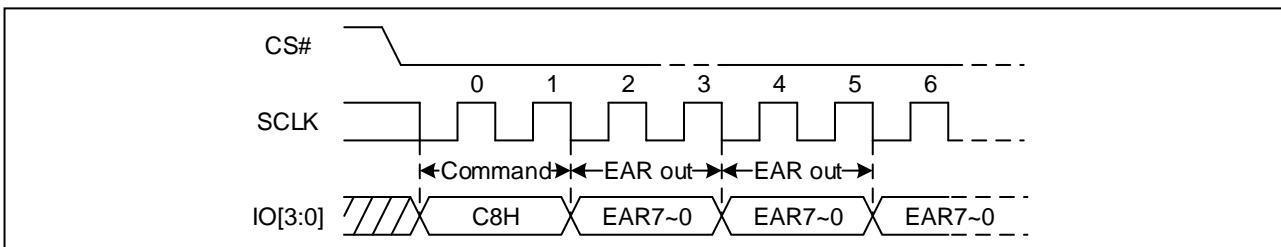

| 8.13 READ EXTENDED ADDRESS REGISTER (C8H) .....                       | 45        |

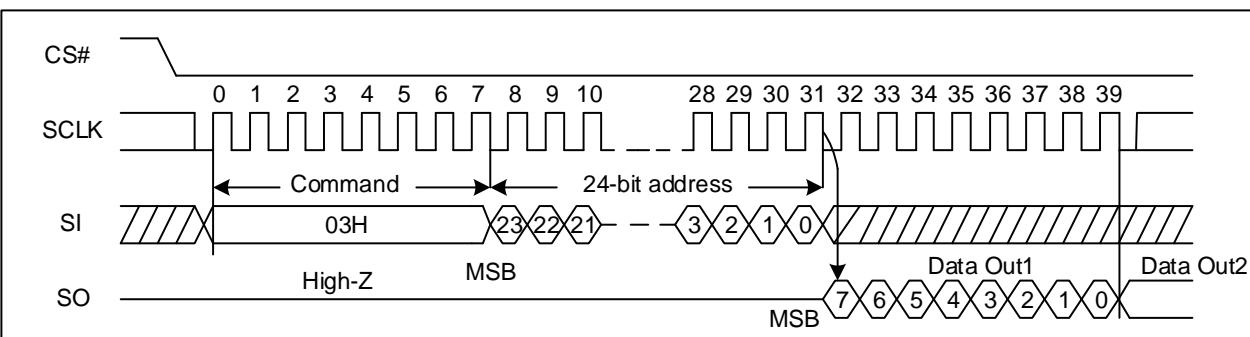

| 8.14 READ DATA BYTES (03H/13H) .....                                  | 45        |

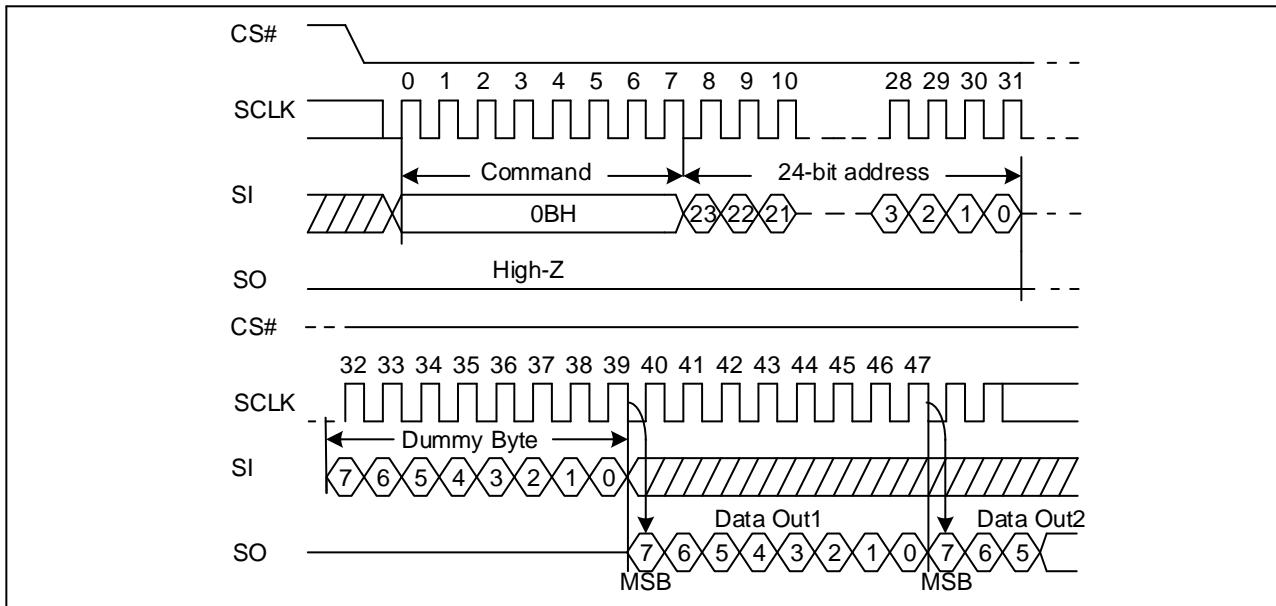

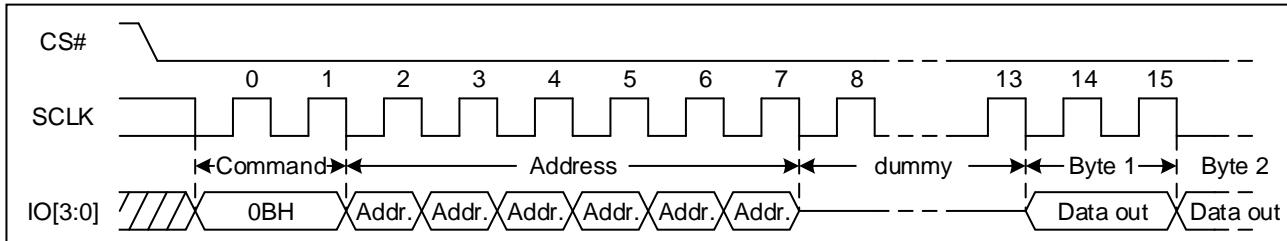

| 8.15 READ DATA BYTES AT HIGHER SPEED (0BH/0CH).....                   | 46        |

| 8.16 DUAL OUTPUT FAST READ (3BH/3CH).....                             | 47        |

| 8.17 QUAD OUTPUT FAST READ (6BH/6CH) .....                            | 47        |

| 8.18 DUAL I/O FAST READ (BBH/BCH).....                                | 48        |

|           |                                                                              |           |

|-----------|------------------------------------------------------------------------------|-----------|

| 8.19      | QUAD I/O FAST READ (EBH/ECH) .....                                           | 50        |

| 8.20      | BURST READ WITH WRAP (0CH).....                                              | 51        |

| 8.21      | SET BURST WITH WRAP (77H) .....                                              | 51        |

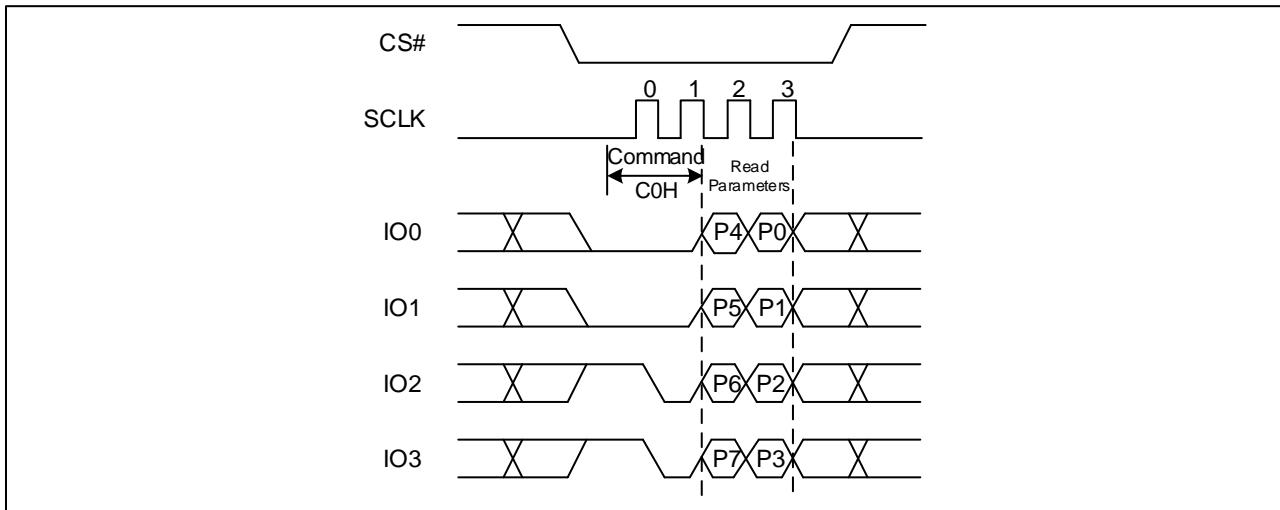

| 8.22      | SET READ PARAMETERS (COH) .....                                              | 52        |

| 8.23      | PAGE PROGRAM (PP) (02H/12H).....                                             | 53        |

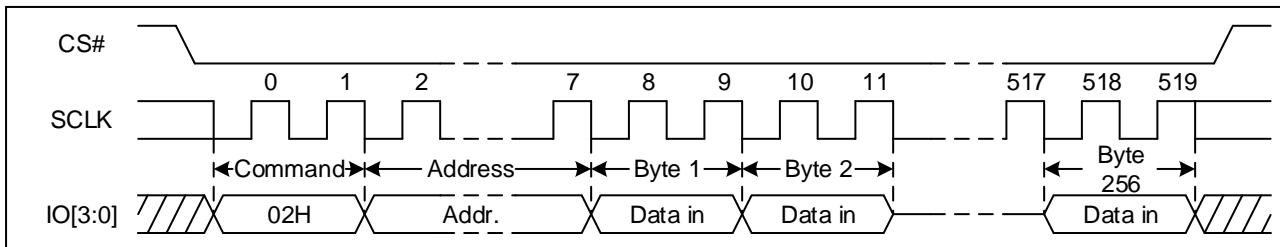

| 8.24      | QUAD PAGE PROGRAM (32H/34H).....                                             | 54        |

| 8.25      | SECTOR ERASE (SE) (20H/21H).....                                             | 55        |

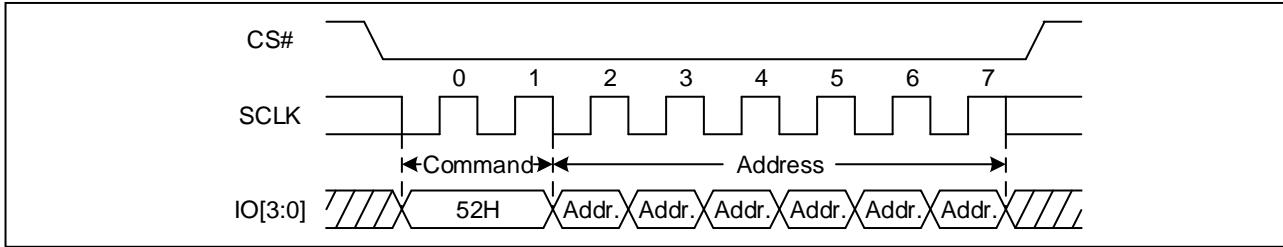

| 8.26      | 32KB BLOCK ERASE (BE32) (52H/5CH).....                                       | 56        |

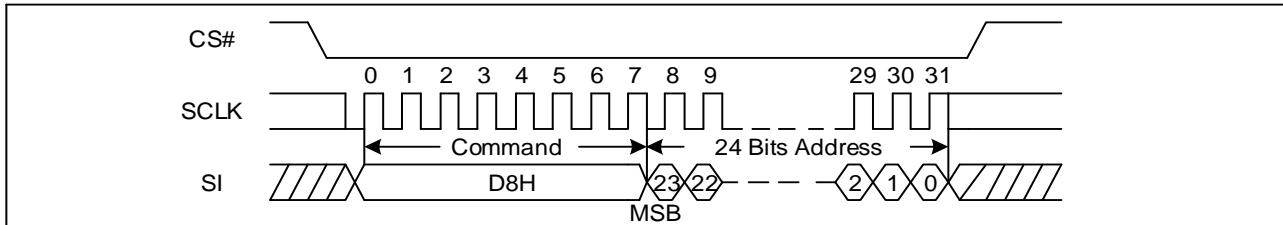

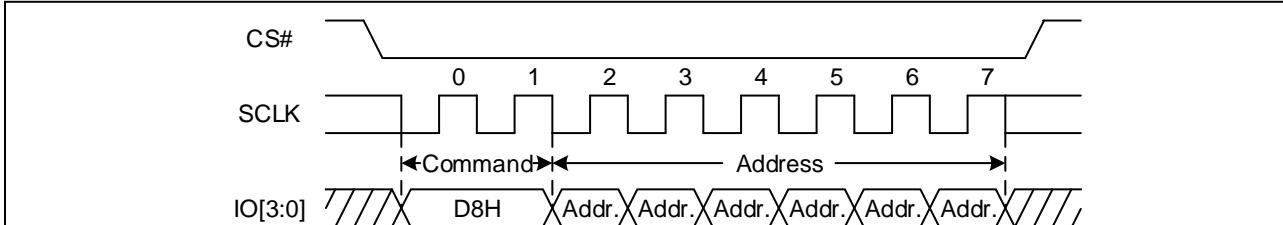

| 8.27      | 64KB BLOCK ERASE (BE64) (D8H/DCH) .....                                      | 57        |

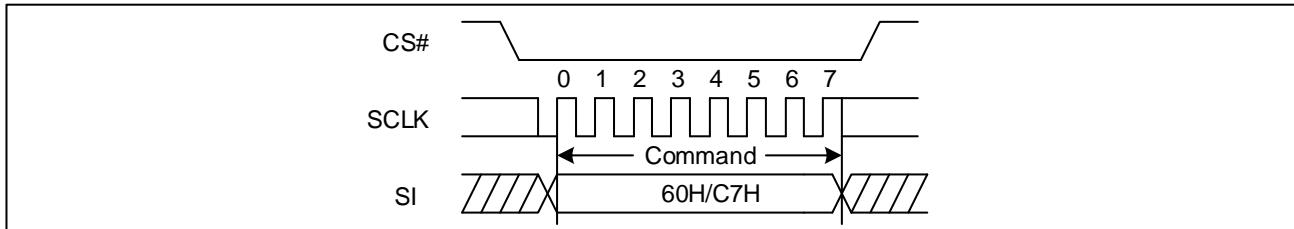

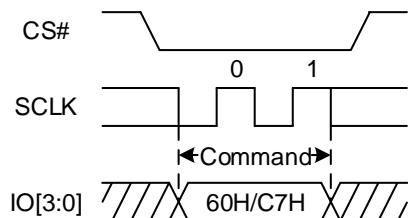

| 8.28      | CHIP ERASE (CE) (60H/C7H) .....                                              | 57        |

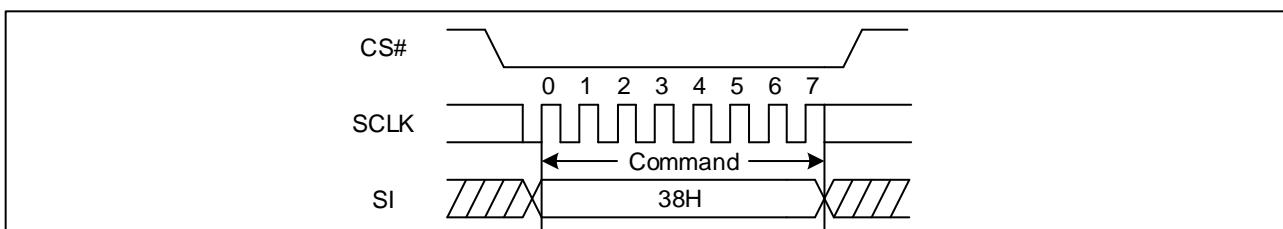

| 8.29      | ENABLE QPI (38H) .....                                                       | 58        |

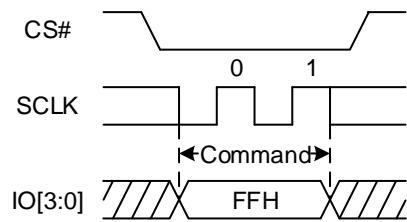

| 8.30      | DISABLE QPI (FFH) .....                                                      | 58        |

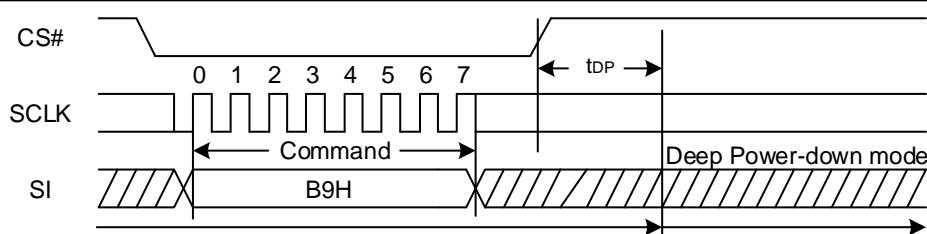

| 8.31      | DEEP POWER-DOWN (DP) (B9H) .....                                             | 59        |

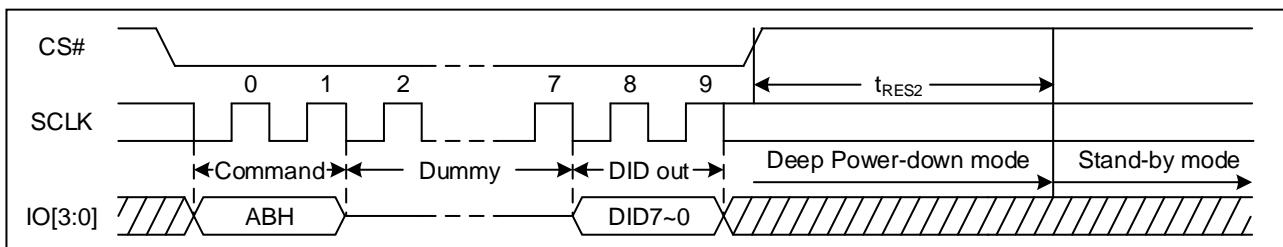

| 8.32      | RELEASE FROM DEEP POWER-DOWN (ABH) .....                                     | 59        |

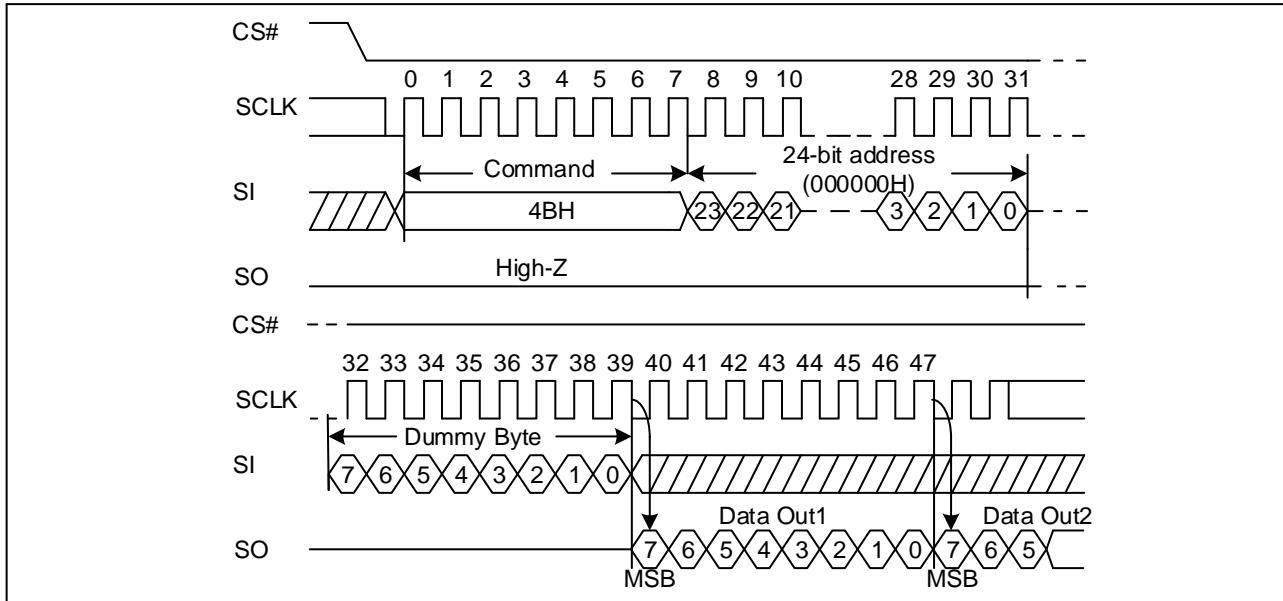

| 8.33      | READ UNIQUE ID (4BH).....                                                    | 60        |

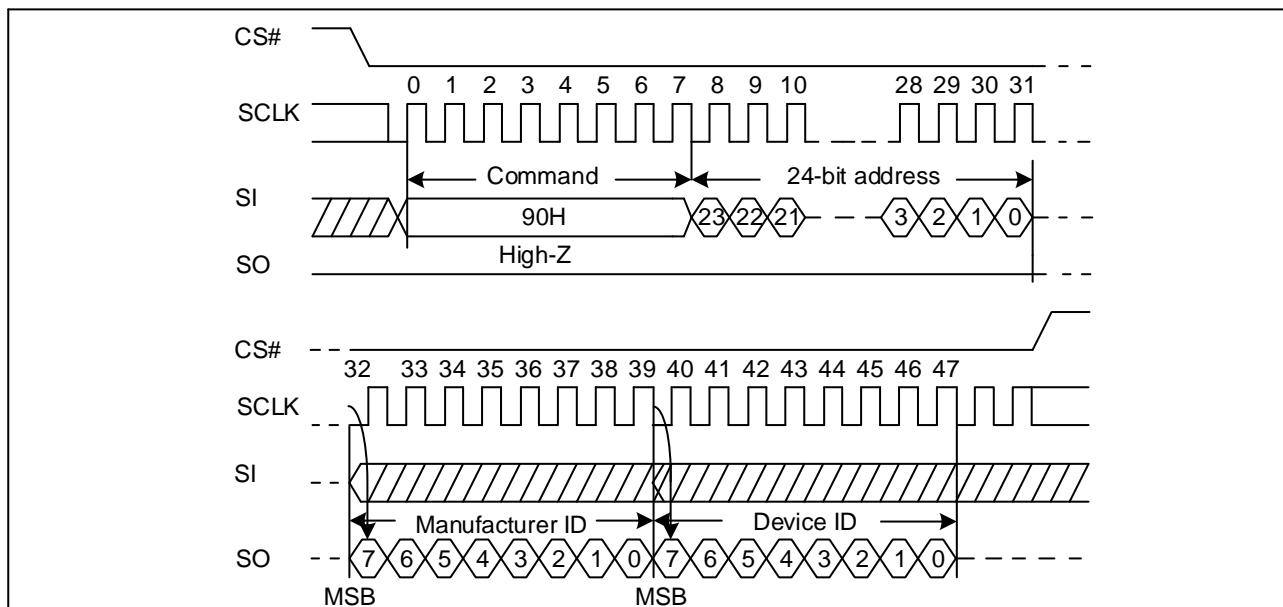

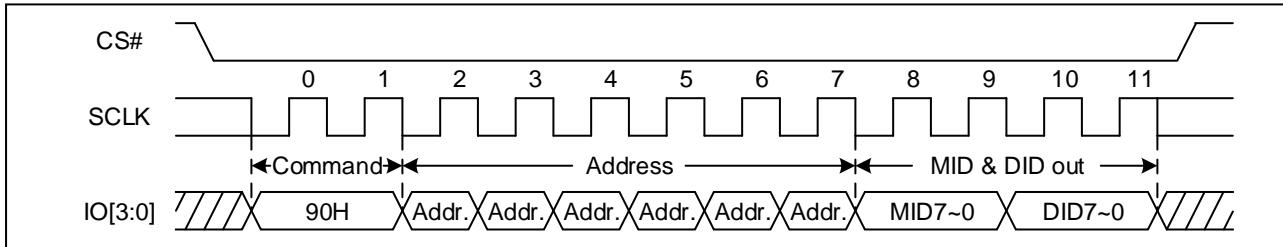

| 8.34      | READ MANUFACTURE ID/ DEVICE ID (REMS) (90H) .....                            | 61        |

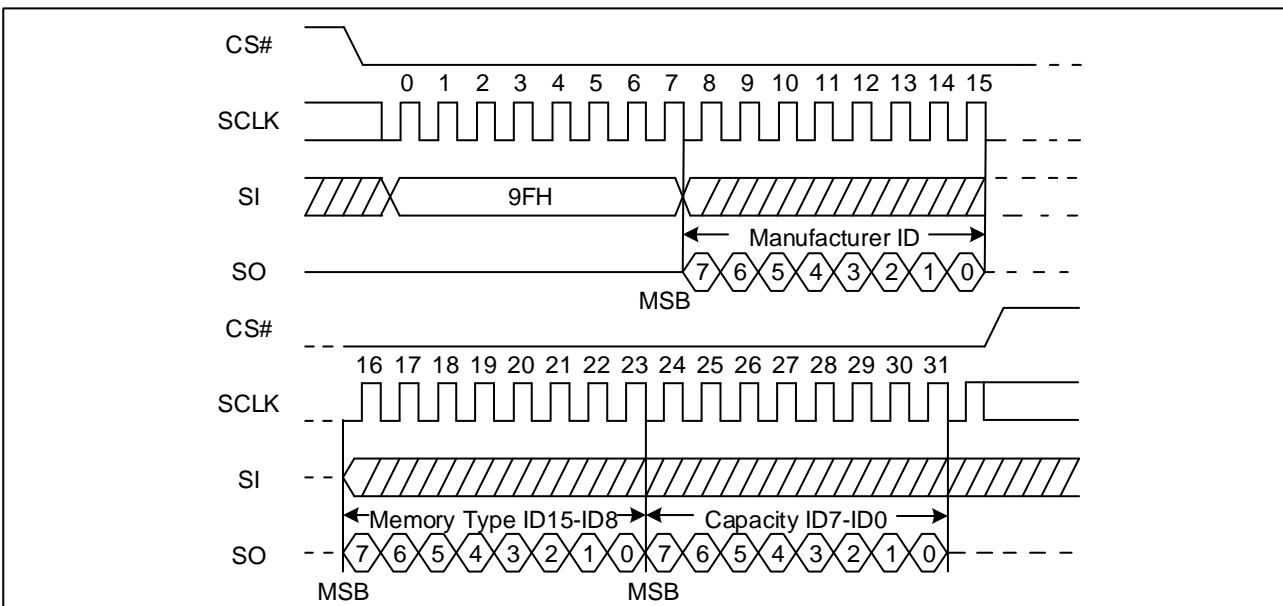

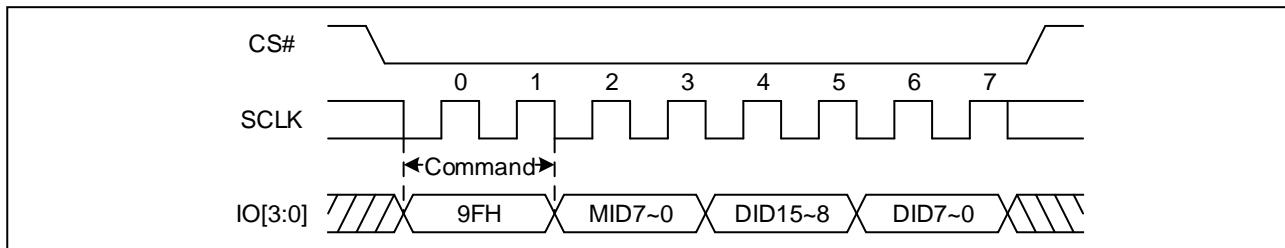

| 8.35      | READ IDENTIFICATION (RDID) (9FH) .....                                       | 62        |

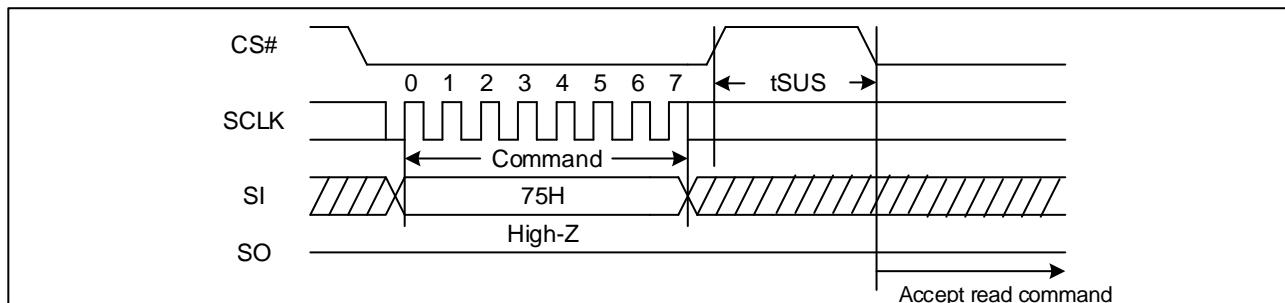

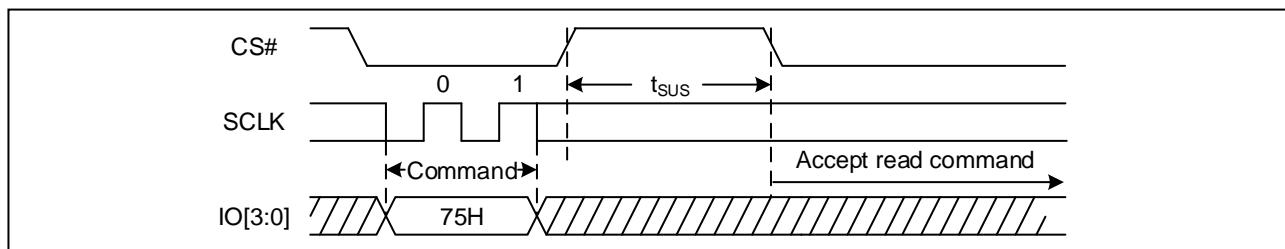

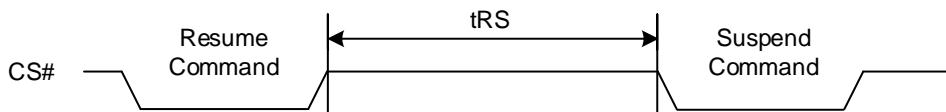

| 8.36      | PROGRAM/ERASE SUSPEND (PES) (75H) .....                                      | 63        |

| 8.37      | PROGRAM/ERASE RESUME (PER) (7AH) .....                                       | 63        |

| 8.38      | ERASE SECURITY REGISTERS (44H) .....                                         | 64        |

| 8.39      | PROGRAM SECURITY REGISTERS (42H).....                                        | 65        |

| 8.40      | READ SECURITY REGISTERS (48H) .....                                          | 65        |

| 8.41      | GLOBAL BLOCK/SECTOR LOCK (7EH) OR UNLOCK (98H).....                          | 66        |

| 8.42      | SET NONVOLATILE LOCK REGISTER (E3H) .....                                    | 67        |

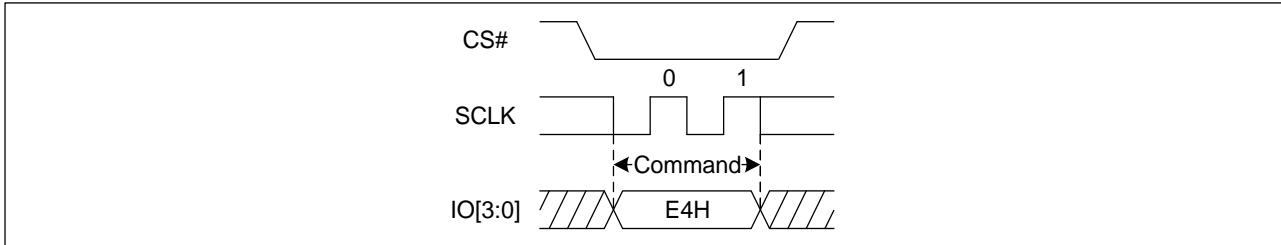

| 8.43      | CLEAR ALL NONVOLATILE LOCK REGISTERS (E4H).....                              | 68        |

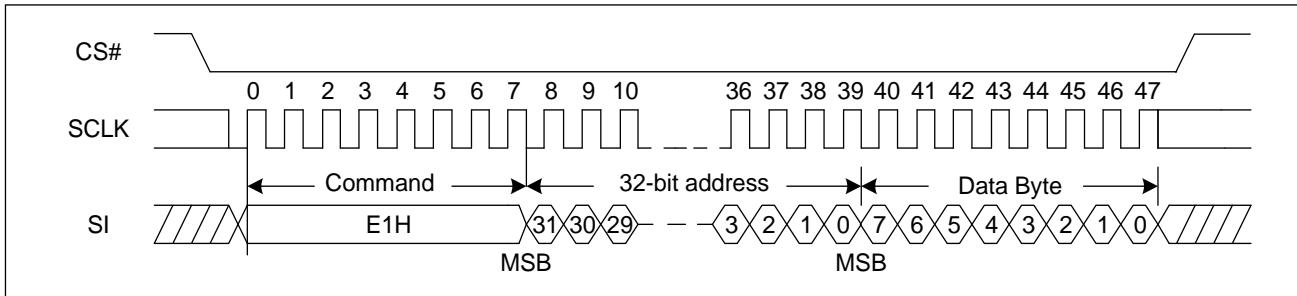

| 8.44      | WRITE VOLATILE LOCK REGISTER (E1H) .....                                     | 69        |

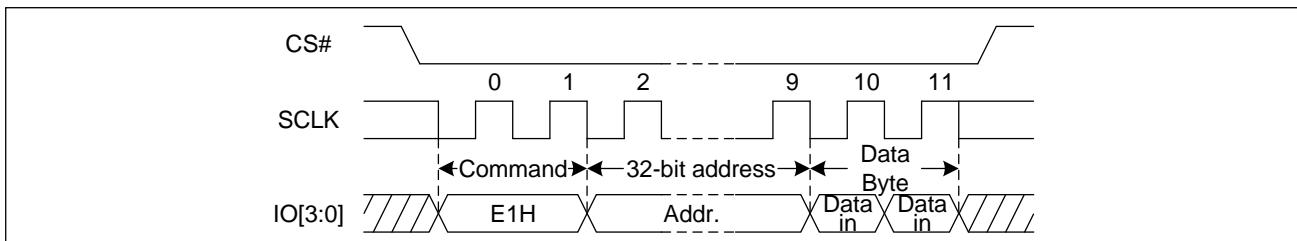

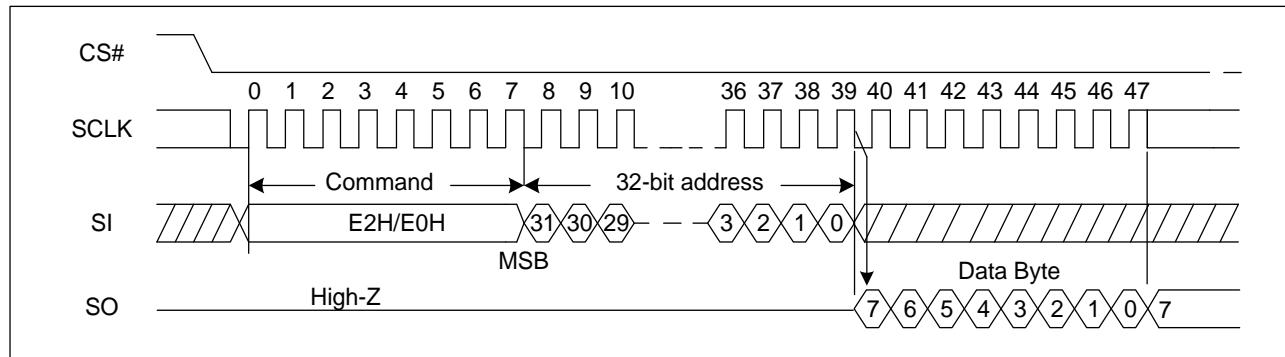

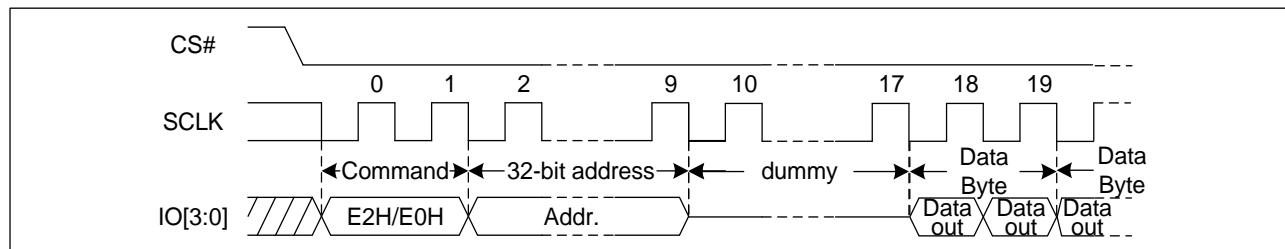

| 8.45      | READ NONVOLATILE LOCK REGISTER (E2H) / READ VOLATILE LOCK REGISTER(E0H)..... | 70        |

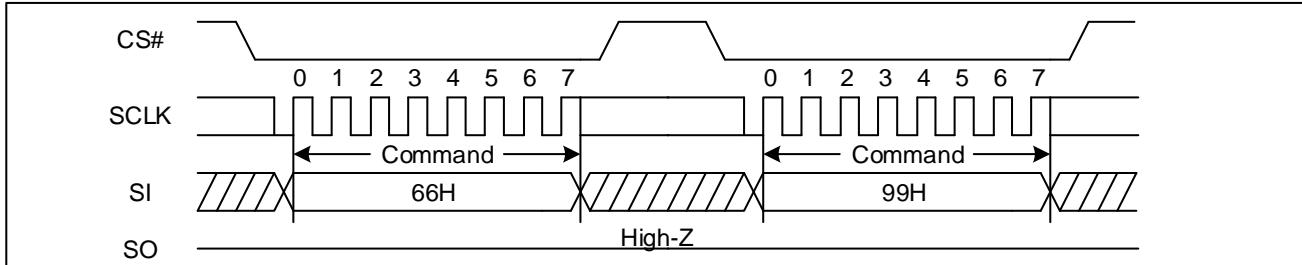

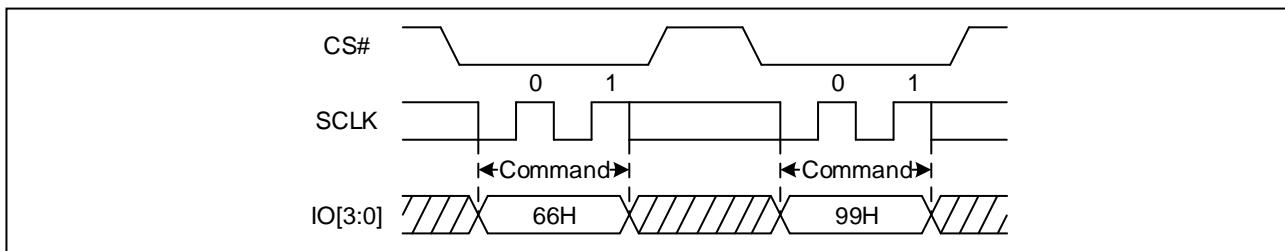

| 8.46      | ENABLE RESET (66H) AND RESET (99H).....                                      | 70        |

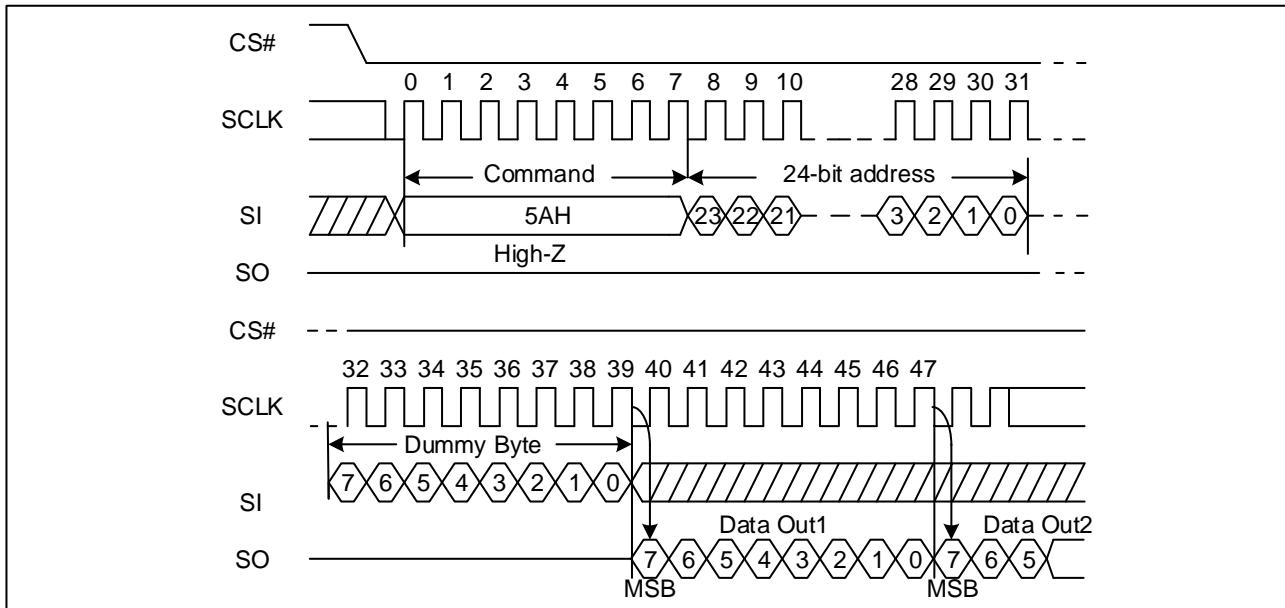

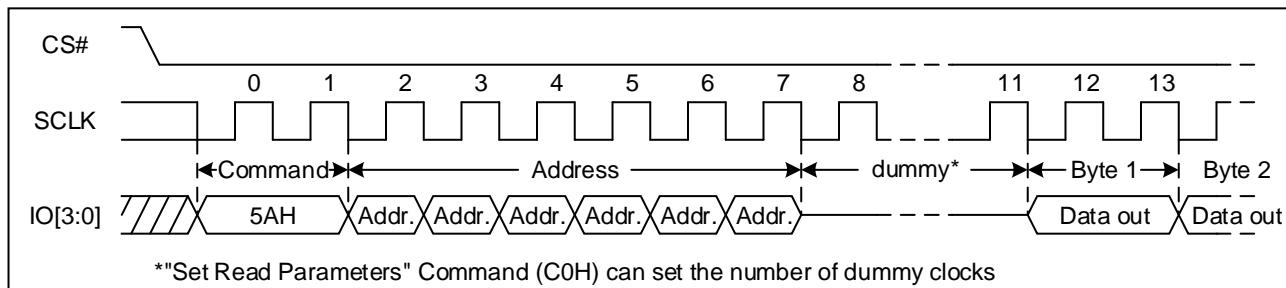

| 8.47      | READ SERIAL FLASH DISCOVERABLE PARAMETER (5AH).....                          | 71        |

| <b>9</b>  | <b>ELECTRICAL CHARACTERISTICS .....</b>                                      | <b>73</b> |

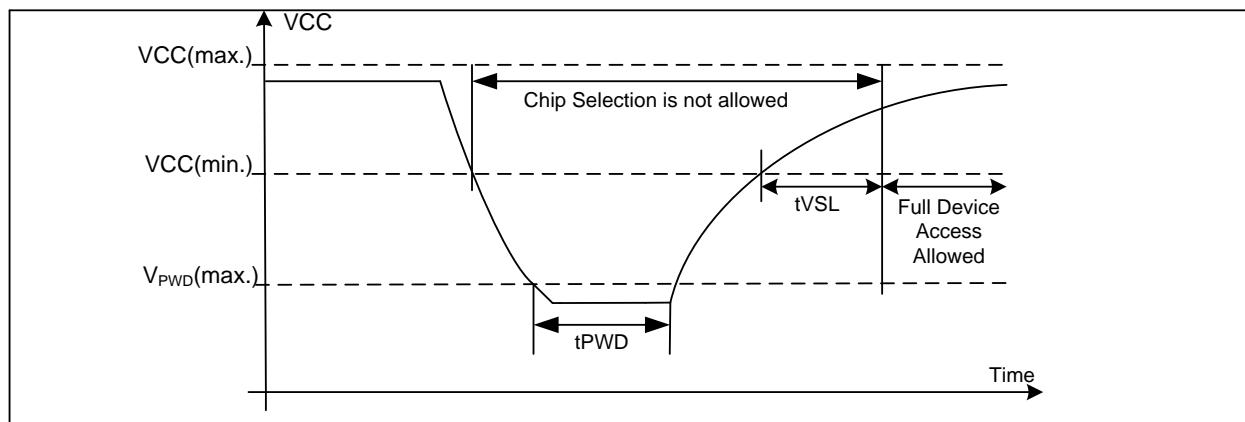

| 9.1       | POWER-ON TIMING .....                                                        | 73        |

| 9.2       | INITIAL DELIVERY STATE .....                                                 | 73        |

| 9.3       | ABSOLUTE MAXIMUM RATINGS .....                                               | 73        |

| 9.4       | CAPACITANCE MEASUREMENT CONDITIONS.....                                      | 74        |

| 9.5       | DC CHARACTERISTICS .....                                                     | 75        |

| 9.6       | AC CHARACTERISTICS .....                                                     | 78        |

| <b>10</b> | <b>ORDERING INFORMATION.....</b>                                             | <b>85</b> |

| 10.1      | VALID PART NUMBERS .....                                                     | 86        |

| <b>11</b> | <b>PACKAGE INFORMATION .....</b>                                             | <b>87</b> |

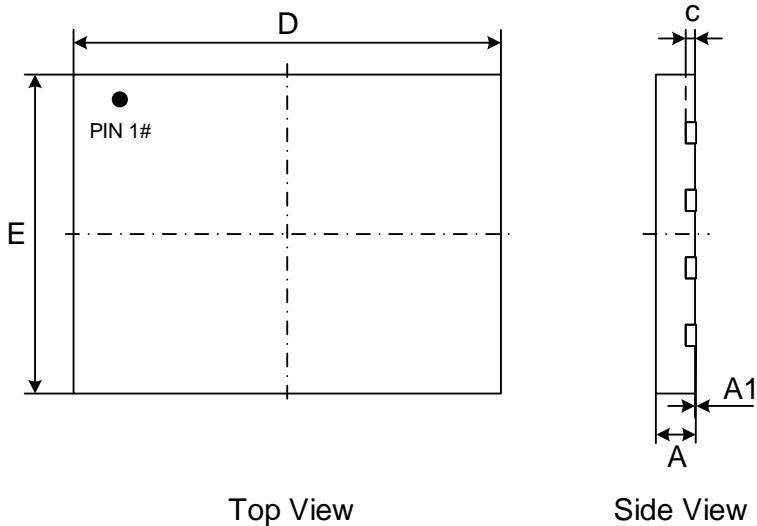

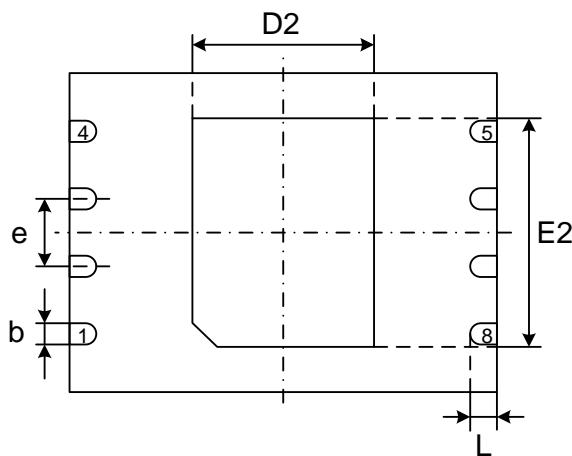

| 11.1      | PACKAGE WSON8 (8x6MM).....                                                   | 87        |

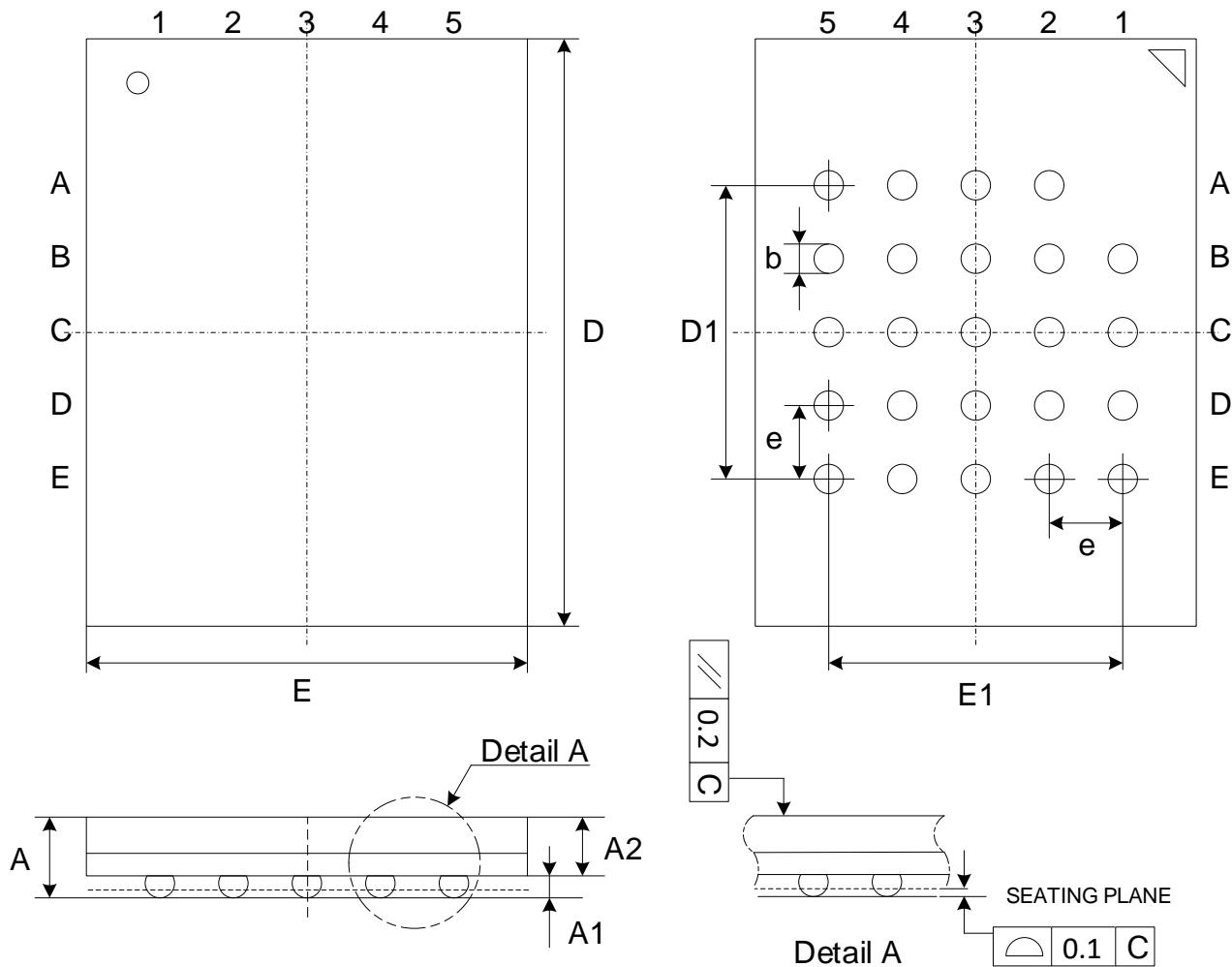

| 11.2      | PACKAGE TFBGA-24BALL (5x5 BALL ARRAY).....                                   | 88        |

GigaDevice

**Uniform Sector

Dual and Quad Serial Flash**

**GD55B01GF**

---

|           |                              |           |

|-----------|------------------------------|-----------|

| 11.3      | PACKAGE SOP16 300MIL .....   | 89        |

| <b>12</b> | <b>REVISION HISTORY.....</b> | <b>90</b> |

## 1 FEATURES

- ◆ 1G-bit Serial NOR Flash Memory

- 128M-Byte

- 256 Bytes per programmable page

- ◆ Standard, Dual, Quad SPI, QPI

- Standard SPI: SCLK, CS#, SI, SO, WP#, RESET#

- Dual SPI: SCLK, CS#, IO0, IO1, WP#, RESET#

- Quad SPI: SCLK, CS#, IO0, IO1, IO2, IO3, RESET#

- QPI: SCLK, CS#, IO0, IO1, IO2, IO3, RESET#

- 3 or 4-Byte Address Mode

- ◆ High Speed Clock Frequency

- 133MHz for fast read

- Dual I/O Data transfer up to 266Mbits/s

- Quad I/O Data transfer up to 532Mbits/s

- QPI Mode Data transfer up to 532Mbits/s

- ◆ Allows XIP (eXecute in Place) Operation

- High speed Read reduce overall XIP instruction fetch time

- Continuous Read with Wrap further reduce data latency to fill up SoC cache

- ◆ Software/Hardware Write Protection

- Write protect all/portion of memory via software

- Enable/Disable protection with WP# Pin

- Individual Block Protection

- ◆ Fast Program/Erase Speed

- Page Program time: 0.18ms typical

- Sector Erase time: 30ms typical

- Block Erase time: 0.12/0.15s typical

- Chip Erase time: 150s typical

- ◆ Flexible Architecture

- Sector of 4K-Byte

- Block of 32/64K-Byte

- Erase/Program Suspend/Resume

- ◆ Low Power Consumption

- 32µA typical stand-by current

- 4µA typical power-down current

- ◆ Advanced Security Features

- 128-bit Unique ID

- 3x4K-Byte Security Registers With OTP Lock

- ◆ Single Power Supply Voltage

- Full voltage range: 2.7~3.6V

- ◆ Endurance and Data Retention

- Minimum 100,000 Program/Erase Cycles

- 20-year data retention typical

- ◆ Package Information

- WSON8 (8x6mm)

- TFBGA-24ball (5x5 Ball Array)

- SOP16 300mil

## 2 GENERAL DESCRIPTIONS

The GD55B01GF (1G-bit) Serial NOR flash supports the standard Serial Peripheral Interface (SPI), and the Dual/Quad SPI: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2, I/O3. The Dual I/O data is transferred with speed of 266Mbit/s, and the Quad I/O data is transferred with speed of 532Mbit/s.

### CONNECTION DIAGRAM AND PIN DESCRIPTION

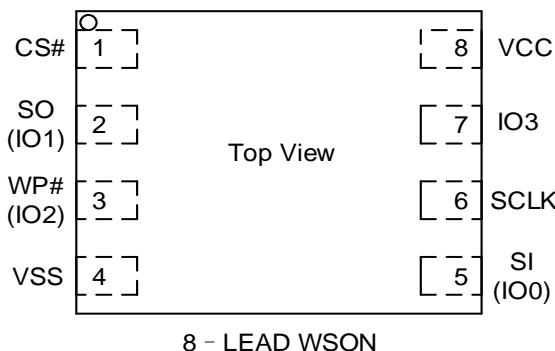

Figure 1 Connection Diagram for WSON8 package

8 - LEAD WSON

Table 1 Pin Description for WSON8 package

| Pin No. | Pin Name  | I/O | Description                               |

|---------|-----------|-----|-------------------------------------------|

| 1       | CS#       | I   | Chip Select Input                         |

| 2       | SO (IO1)  | I/O | Data Output (Data Input Output 1)         |

| 3       | WP# (IO2) | I/O | Write Protect Input (Data Input Output 2) |

| 4       | VSS       |     | Ground                                    |

| 5       | SI (IO0)  | I/O | Data Input (Data Input Output 0)          |

| 6       | SCLK      | I   | Serial Clock Input                        |

| 7       | IO3       | I/O | Data Input Output 3                       |

| 8       | VCC       |     | Power Supply                              |

Note:

1. CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

2. WP# functions are only available for Standard/Dual SPI.

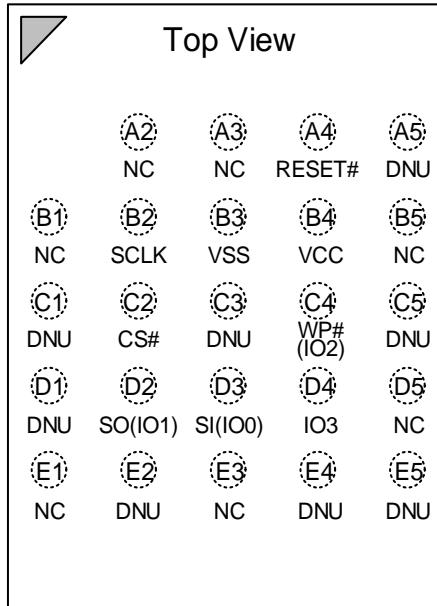

**Figure 2 Connection Diagram for TFBGA24 5x5 ball array package**

**24-BALL TFBGA (5x5 ball array)**

**Table 2 Ball Description for TFBGA24 5x5 ball array package**

| Pin No.                     | Pin Name  | I/O | Description                                           |

|-----------------------------|-----------|-----|-------------------------------------------------------|

| A4                          | RESET#    | I   | Reset Input                                           |

| B2                          | SCLK      | I   | Serial Clock Input                                    |

| B3                          | VSS       |     | Ground                                                |

| B4                          | VCC       |     | Power Supply                                          |

| C2                          | CS#       | I   | Chip Select Input                                     |

| C4                          | WP# (IO2) | I/O | Write Protect Input (Data Input Output 2)             |

| A5/C1/C3/C5/<br>D1/E2/E4/E5 | DNU       |     | Do Not Use (It may connect to internal signal inside) |

| D2                          | SO (IO1)  | I/O | Data Output (Data Input Output 1)                     |

| D3                          | SI (IO0)  | I/O | Data Input (Data Input Output 0)                      |

| D4                          | IO3       | I/O | Data Input Output 3                                   |

**Notes:**

1. CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

2. The DNU ball must be floating. It may connect to internal signal inside.

3. The NC ball is not connected to any internal signal. It is OK to connect it to the system ground (GND) or leave it floating.

4. The RESET# pin is a dedicated hardware reset pin regardless of device settings or operation states. If the hardware reset function is not used, it is recommended to connect it to VCC in the system but leaving it floating is OK.

5. WP# functions are only available for Standard/Dual SPI.

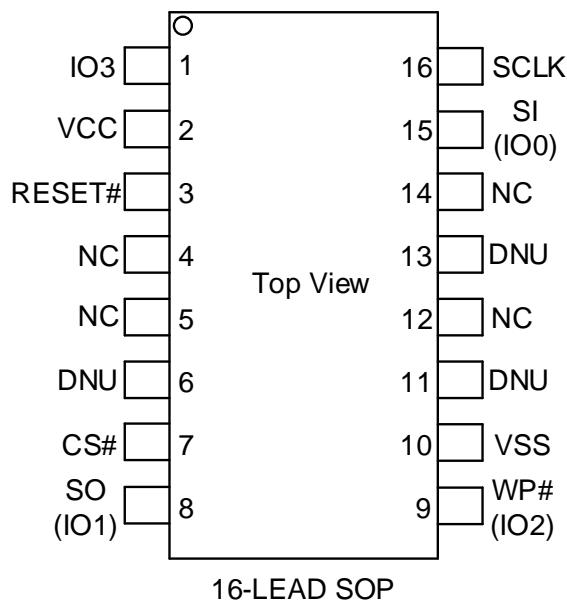

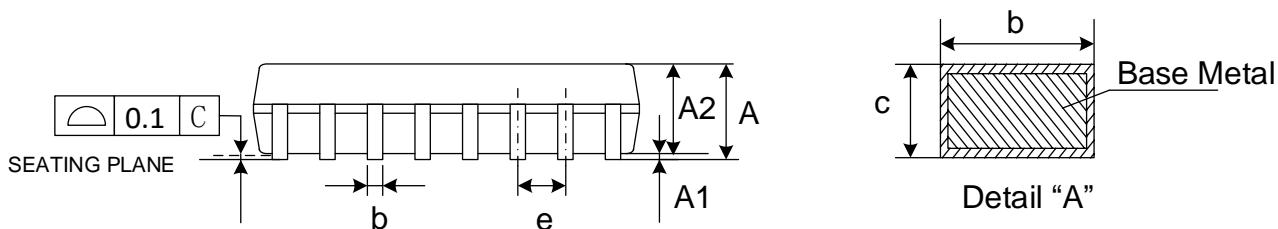

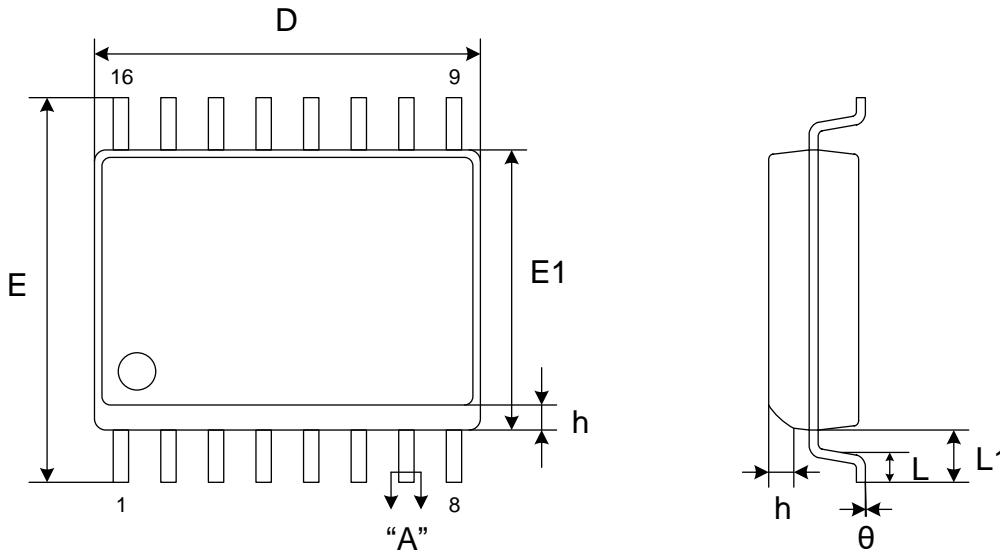

**Figure 3 Connection Diagram for SOP16 package**

**Table 3 Pin Description for SOP16 package**

| Pin No. | Pin Name  | I/O | Description                                           |

|---------|-----------|-----|-------------------------------------------------------|

| 1       | IO3       | I/O | Data Input Output 3                                   |

| 2       | VCC       |     | Power Supply                                          |

| 3       | RESET#    | I   | Reset Input                                           |

| 7       | CS#       | I   | Chip Select Input                                     |

| 8       | SO (IO1)  | I/O | Data Output (Data Input Output 1)                     |

| 9       | WP# (IO2) | I/O | Write Protect Input (Data Input Output 2)             |

| 10      | VSS       |     | Ground                                                |

| 6/11/13 | DNU       |     | Do Not Use (It may connect to internal signal inside) |

| 15      | SI (IO0)  | I/O | Data Input (Data Input Output 0)                      |

| 16      | SCLK      | I   | Serial Clock Input                                    |

**Notes:**

1. CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

2. The DNU pin must be floating. It may connect to internal signal inside.

3. The NC pin is not connected to any internal signal. It is OK to connect it to the system ground (GND) or leave it floating.

4. The RESET# pin is a dedicated hardware reset pin regardless of device settings or operation states. If the hardware reset function is not used, it is recommended to connect it to VCC in the system but leaving it floating is OK.

5. WP# functions are only available for Standard/Dual SPI.

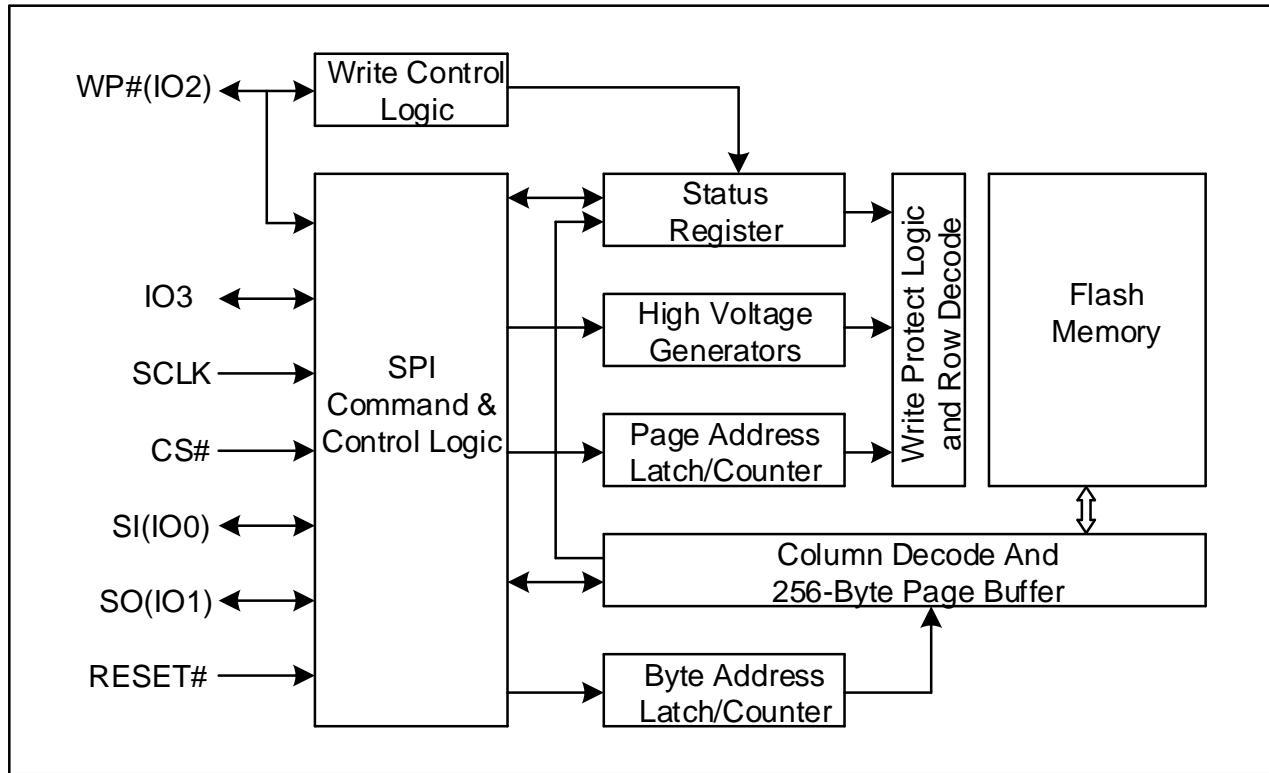

BLOCK DIAGRAM

### 3 MEMORY ORGANIZATION

#### GD55B01GF

| Each device has | Each block has | Each sector has | Each page has |         |

|-----------------|----------------|-----------------|---------------|---------|

| 128M            | 64/32K         | 4K              | 256           | Bytes   |

| 512K            | 256/128        | 16              | -             | pages   |

| 32K             | 16/8           | -               | -             | sectors |

| 2K/4K           | -              | -               | -             | blocks  |

#### UNIFORM BLOCK SECTOR ARCHITECTURE

##### GD55B01GF 64K Bytes Block Sector Architecture

| Block | Sector | Address range |           |

|-------|--------|---------------|-----------|

| 2047  | 32767  | 7FFF000H      | 7FFFFFFH  |

|       | .....  | .....         | .....     |

|       | 32752  | 7FF0000H      | 7FF0FFFFH |

| 2046  | 32751  | 7FEF000H      | 7FEFFFFH  |

|       | .....  | .....         | .....     |

|       | 32736  | 7FE0000H      | 7FE0FFFH  |

| ..... | .....  | .....         | .....     |

|       | .....  | .....         | .....     |

|       | .....  | .....         | .....     |

| ..... | .....  | .....         | .....     |

|       | .....  | .....         | .....     |

|       | .....  | .....         | .....     |

| 2     | 47     | 02F000H       | 02FFFFFFH |

|       | .....  | .....         | .....     |

|       | 32     | 020000H       | 020FFFFH  |

| 1     | 31     | 01F000H       | 01FFFFFFH |

|       | .....  | .....         | .....     |

|       | 16     | 010000H       | 010FFFFH  |

| 0     | 15     | 00F000H       | 00FFFFFFH |

|       | .....  | .....         | .....     |

|       | 0      | 000000H       | 000FFFFH  |

## 4 DEVICE OPERATIONS

### 4.1 SPI Mode

#### Standard SPI

The GD55B01GF features a serial peripheral interface on 4 signals bus: Serial Clock (SCLK), Chip Select (CS#), Serial Data Input (SI) and Serial Data Output (SO). Both SPI bus mode 0 and 3 are supported. Input data is latched on the rising edge of SCLK and data shifts out on the falling edge of SCLK.

#### Dual SPI

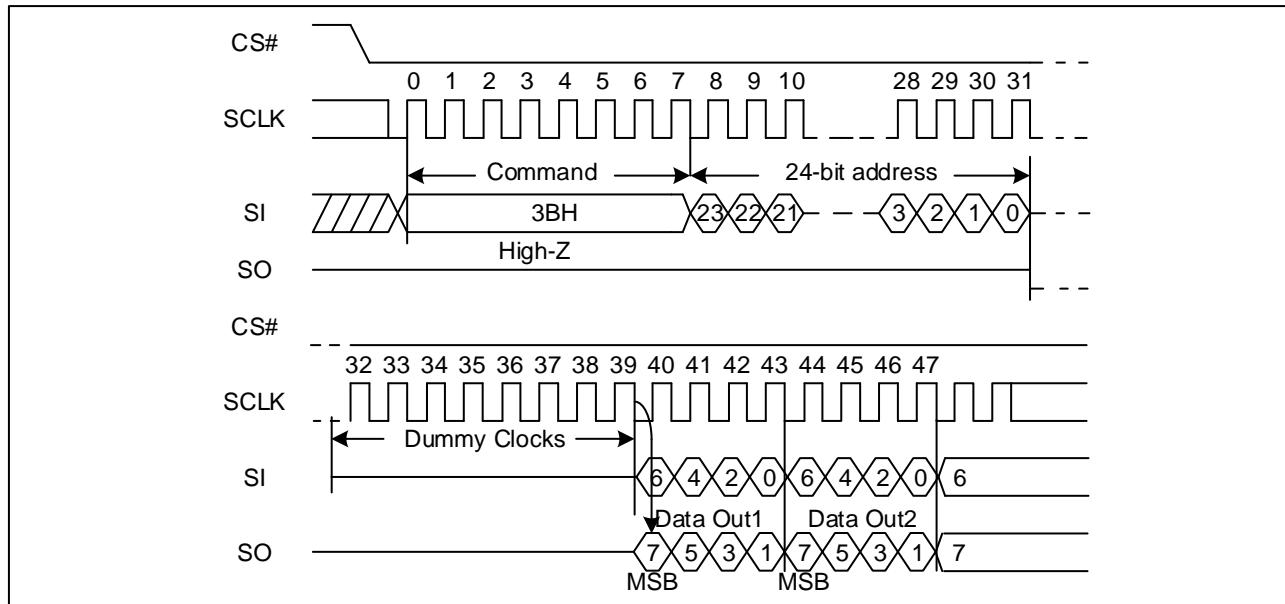

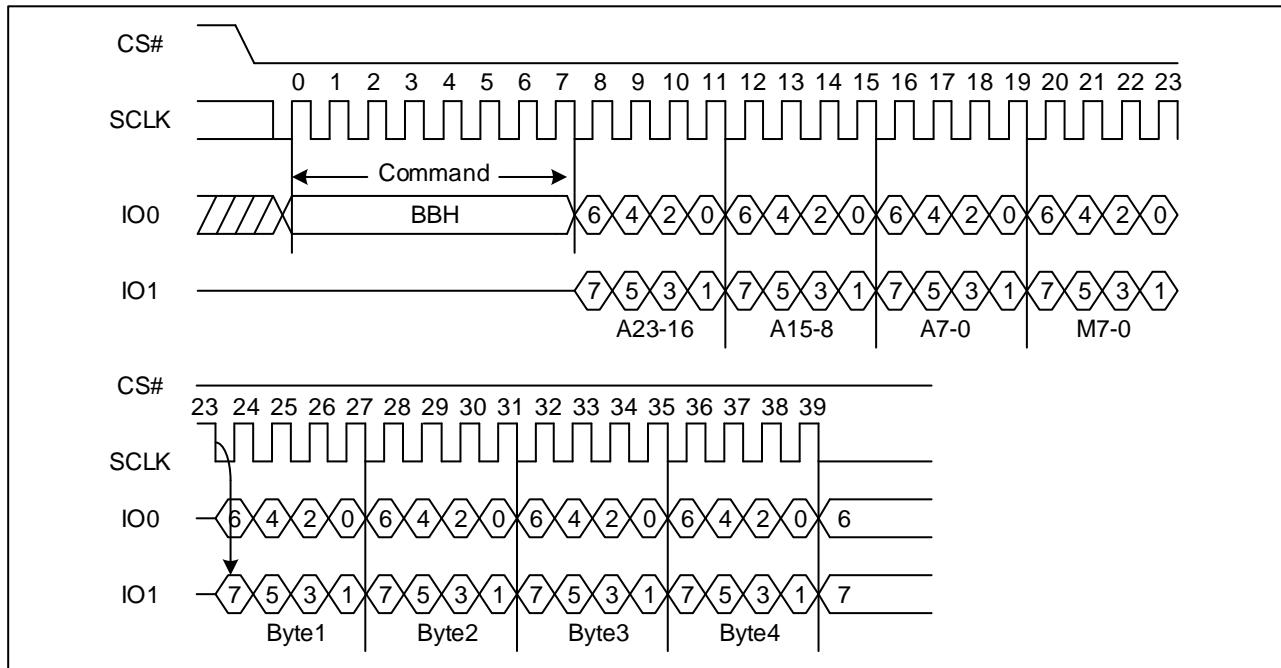

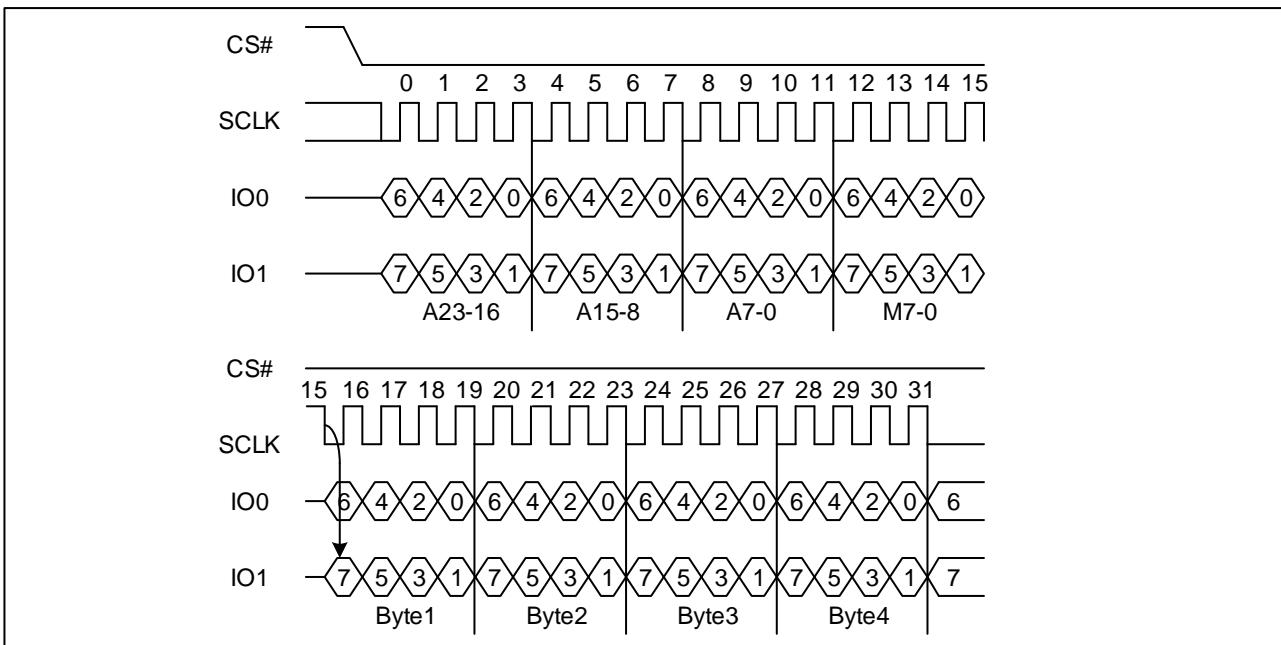

The GD55B01GF supports Dual SPI operation when using the “Dual Output Fast Read”, “Dual Output Fast Read with 4-Byte address”, “Dual I/O Fast Read” and “Dual I/O Fast Read with 4-Byte address” commands (3BH, 3CH, BBH and BCH). These commands allow data to be transferred to or from the device at twice the rate of the standard SPI. When using the Dual SPI command, the SI and SO pins become bidirectional I/O pins: IO0 and IO1.

#### Quad SPI

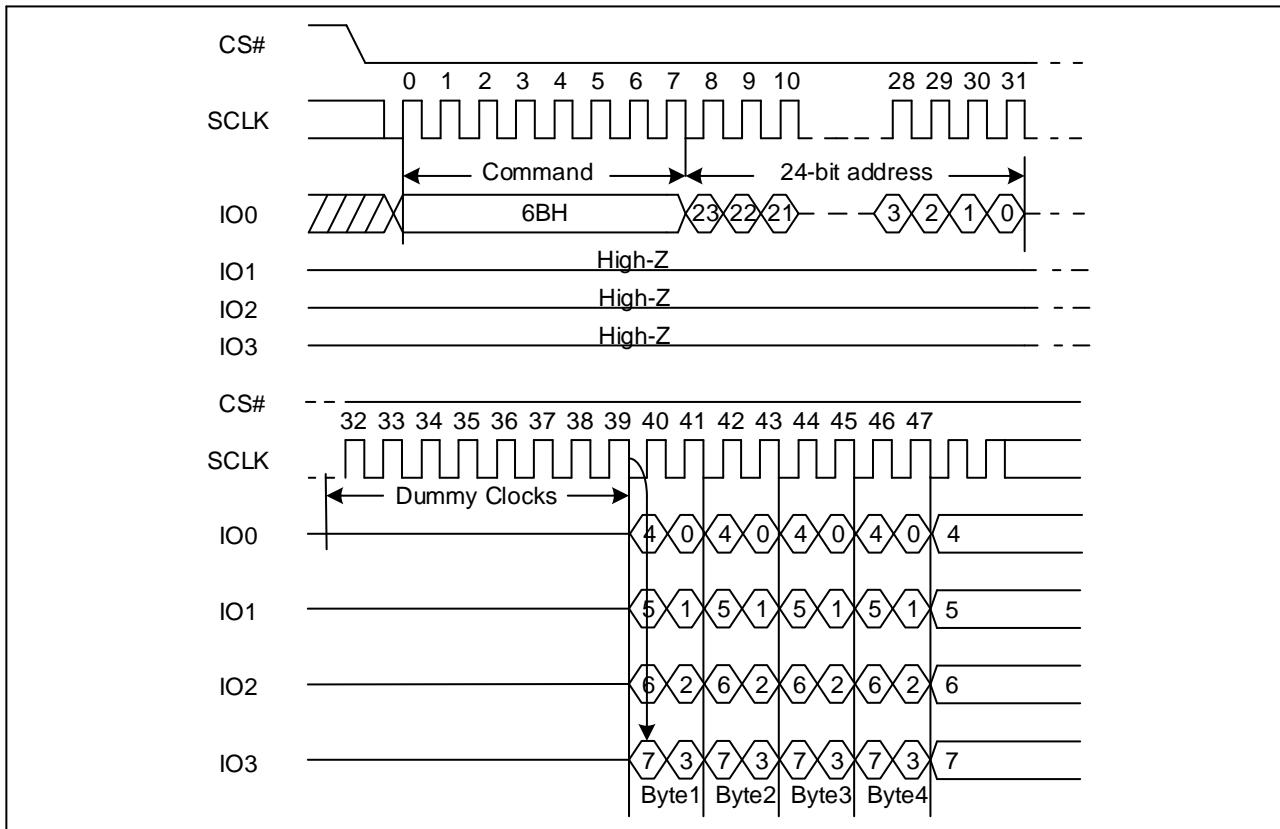

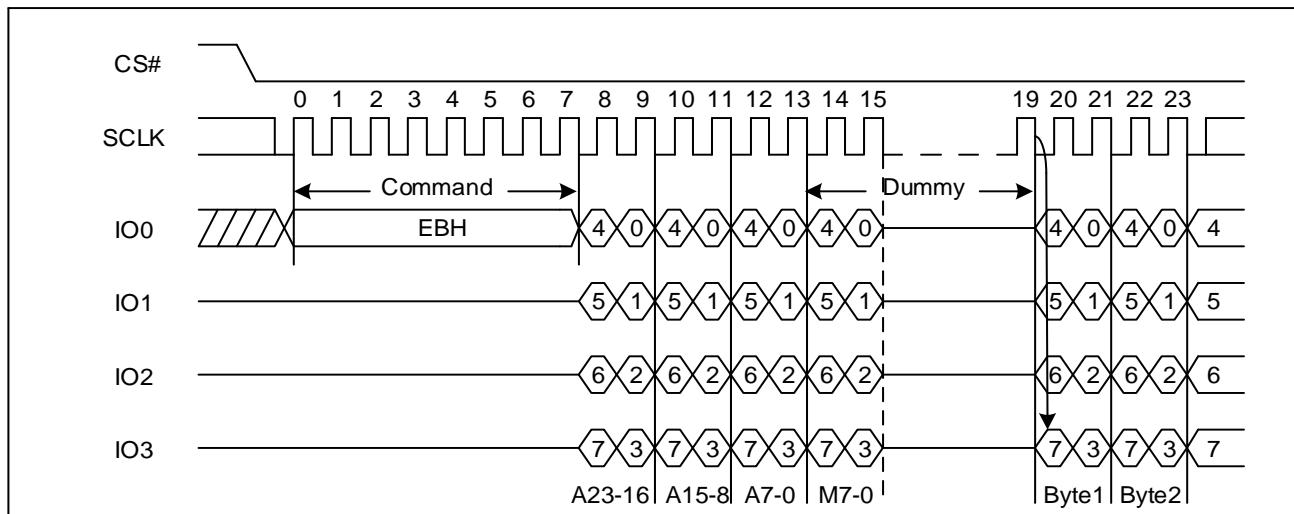

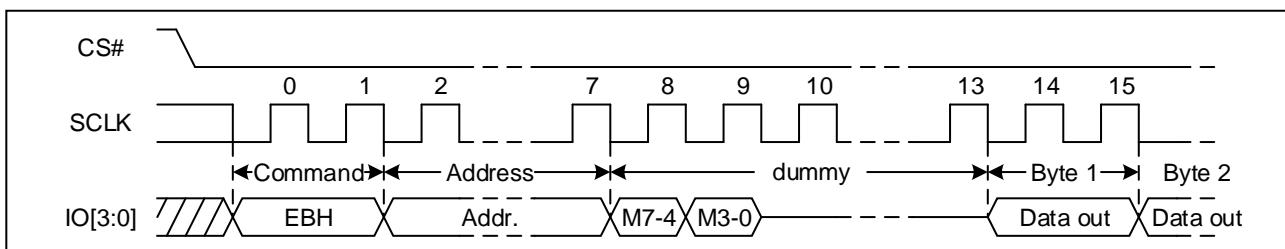

The GD55B01GF supports Quad SPI operation when using the “Quad Output Fast Read”, “Quad I/O Fast Read”, “Quad Page Program” (6BH/6CH, EBH/ECH, 32H/34H) commands. These commands allow data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command the SI and SO pins become bidirectional I/O pins: IO0 and IO1, and the WP# pin become bidirectional I/O pins: IO2.

### 4.2 QPI Mode

The GD55B01GF supports Quad Peripheral Interface (QPI) operations only when the device is switched from Standard/Dual/Quad SPI mode to QPI mode using the “Enable the QPI (38H)” command. The QPI mode utilizes all four IO pins to input the command code. Standard/Dual/Quad SPI mode and QPI mode are exclusive. Only one mode can be active at any given times. “Enable the QPI (38H)” and “Disable the QPI (FFH)” commands are used to switch between these two modes. Upon power-up and Hardware Reset or after software reset using “Enable Reset (66H) and Reset (99H)” command, the default state of the device is Standard/Dual/Quad SPI mode.

### 4.3 RESET Function

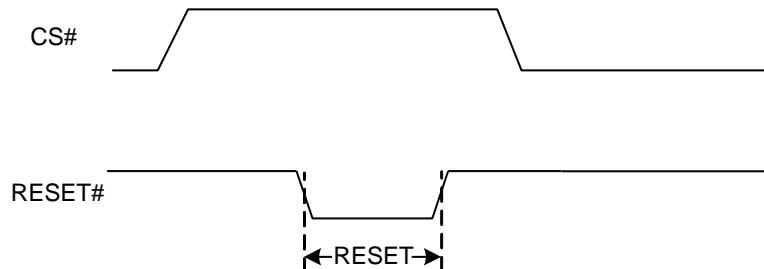

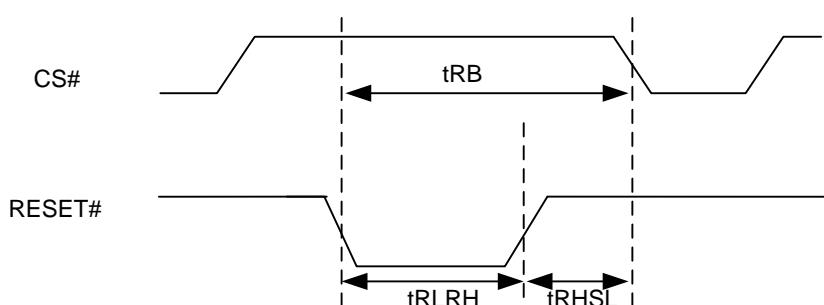

The RESET# pin allows the device to be reset by the control.

The RESET# pin goes low for a minimum period of tRLRH will reset the flash. After reset cycle, the flash is at the following states:

- Standby mode

- All the volatile bits will return to the default status as power on.

Figure 4 RESET Condition

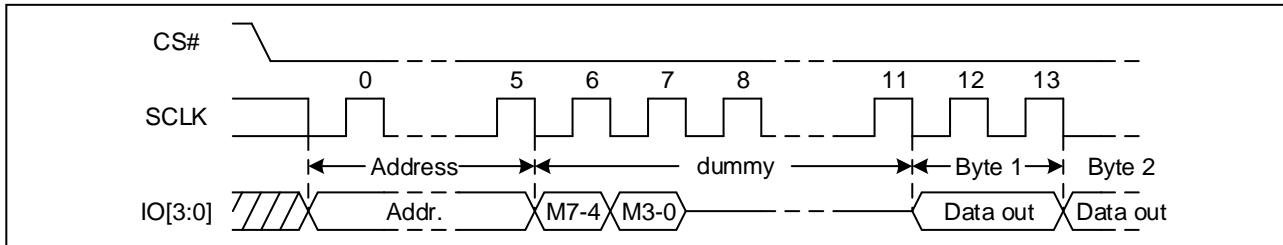

#### 4.4 Enter XIP Mode Directly After Power-On (POR-XIP)

The device can be operated in the selected XIP mode immediately after power-on reset. The XIP mode after Power-on is set by Nonvolatile Configuration Register bits in Byte<0>. Because the device boots directly in XIP, after the power cycle, no command code is necessary. XIP is terminated by setting the “Continuous Read Mode” bits (M5-4) do not equal (1, 0).

## 5 DATA PROTECTION

The GD55B01GF provides the following data protection methods:

- ◆ Write Enable (WREN) command: The WREN command sets the Write Enable Latch (WEL) bit to '1'. The WEL bit will reset to '0' after the following sequence or instructions:

- Power-Up/ Software Reset (66H+99H)/Hardware Reset

- Write Disable (WRDI)

- Write Status Register (WRSR 1, 2 & 3)

- Write Extended Address Register (WEAR)

- Write Nonvolatile Configuration Register (WNVCR)

- Write Volatile Configuration Register (WVCR)

- Page Program (PP)

- Sector Erase (SE) / Block Erase (BE) / Chip Erase (CE) / Erase Security Registers / Program Security Registers

- Advanced Block Protection related instructions: Set Nonvolatile Lock (NL) Register, Clear All Nonvolatile Lock (NL) Registers, Write Volatile Lock (VL) Register

- ◆ Software Protection Mode:

- The Block Protect (BP4, BP3, BP2, BP1, and BP0 along with the CMP) bits define the section of the memory array that can be read but cannot be changed.

- Nonvolatile Lock (NL) Registers are additional memory non-volatile lock registers that can protect or unprotect a memory with greater granularity at the individual sectors/block level.

- Volatile Lock (VL) Registers like NL Registers serve similar lock bit functionality at individual sector/block level except they are volatile bits.

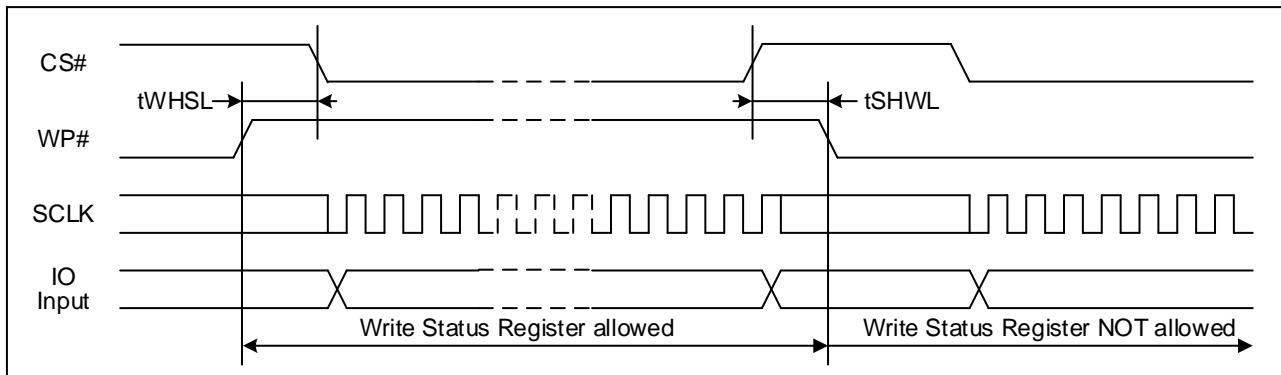

- ◆ Hardware Protection Mode when SRP0 is '1': WP# goes low to protect the Status Register bits (i.e., BP0~BP4, CMP bits) and Nonvolatile Lock (NL) Registers against writes.

- ◆ Deep Power-Down Mode: In Deep Power-Down Mode, all commands are ignored except the Release from Deep Power-Down Mode command and reset command (66H+99H).

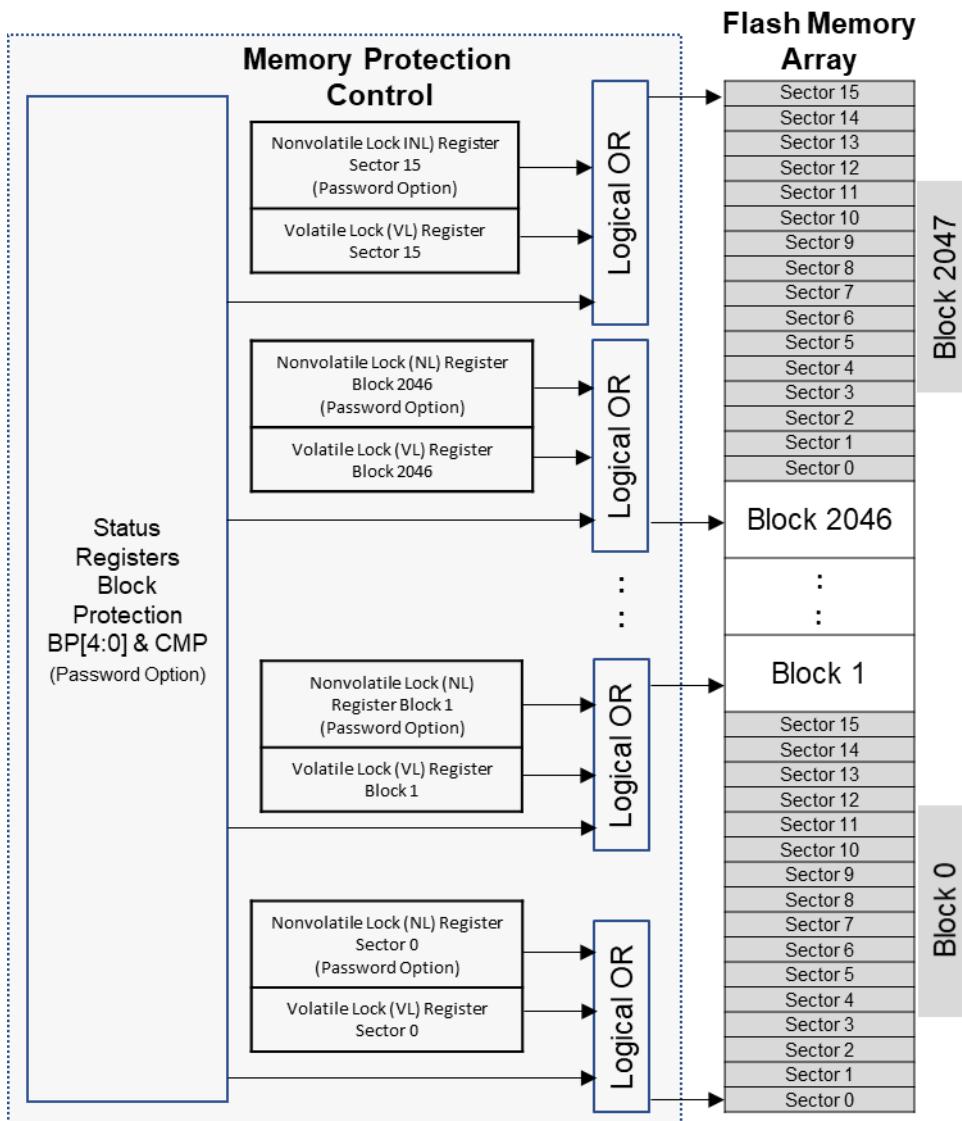

The GD55B01GF device supports several memory protection methods: Block Protection via Block Protect/CMP bits, Individual Volatile Block Lock Protection via VL Register bits, Individual Nonvolatile Block Lock Protection via NL Register Bits. All these protection schemes function in a logical OR method to protect or unprotect targeted sector/block as shown on Figure 5.

**Figure 5 Memory Protection Control Overview**

**Notes:**

1. The first and last blocks will have NL/VL Registers protections at the 4KB sector level. Each 4KB sector in these blocks can be individually locked by NL/VL Registers setting.

2. Each of the middle 64KB blocks has NL/VL Registers protections at the 64KB block level. Each 64KB block can be individually locked by NL/VL Registers setting.

Status Register Block Protection (BP4, BP3, BP2, BP1, BP0, CMP)

Table 4. GD55B01GF Protected area size (CMP=0)

| Status Register Content |     |     |     |     | Memory Content |                     |         |              |

|-------------------------|-----|-----|-----|-----|----------------|---------------------|---------|--------------|

| BP4                     | BP3 | BP2 | BP1 | BP0 | Blocks         | Addresses           | Density | Portion      |

| X                       | 0   | 0   | 0   | 0   | NONE           | NONE                | NONE    | NONE         |

| 0                       | 0   | 0   | 0   | 1   | 2047           | 07FF0000h-07FFFFFFh | 64KB    | Upper 1/2048 |

| 0                       | 0   | 0   | 1   | 0   | 2046 to 2047   | 07FE0000h-07FFFFFFh | 128KB   | Upper 1/1024 |

| 0                       | 0   | 0   | 1   | 1   | 2044 to 2047   | 07FC0000h-07FFFFFFh | 256KB   | Upper 1/512  |

| 0                       | 0   | 1   | 0   | 0   | 2040 to 2047   | 07F80000h-07FFFFFFh | 512KB   | Upper 1/256  |

| 0                       | 0   | 1   | 0   | 1   | 2032 to 2047   | 07F00000h-07FFFFFFh | 1MB     | Upper 1/128  |

| 0                       | 0   | 1   | 1   | 0   | 2016 to 2047   | 07E00000h-07FFFFFFh | 2MB     | Upper 1/64   |

| 0                       | 0   | 1   | 1   | 1   | 1984 to 2047   | 07C00000h-07FFFFFFh | 4MB     | Upper 1/32   |

| 0                       | 1   | 0   | 0   | 0   | 1920 to 2047   | 07800000h-07FFFFFFh | 8MB     | Upper 1/16   |

| 0                       | 1   | 0   | 0   | 1   | 1792 to 2047   | 07000000h-07FFFFFFh | 16MB    | Upper 1/8    |

| 0                       | 1   | 0   | 1   | 0   | 1536 to 2047   | 06000000h-07FFFFFFh | 32MB    | Upper 1/4    |

| 0                       | 1   | 0   | 1   | 1   | 1024 to 2047   | 04000000h-07FFFFFFh | 64MB    | Upper 1/2    |

| 1                       | 0   | 0   | 0   | 1   | 0              | 00000000h-0000FFFFh | 64KB    | Lower 1/2048 |

| 1                       | 0   | 0   | 1   | 0   | 0 to 1         | 00000000h-0001FFFFh | 128KB   | Lower 1/1024 |

| 1                       | 0   | 0   | 1   | 1   | 0 to 3         | 00000000h-0003FFFFh | 256KB   | Lower 1/512  |

| 1                       | 0   | 1   | 0   | 0   | 0 to 7         | 00000000h-0007FFFFh | 512KB   | Lower 1/256  |

| 1                       | 0   | 1   | 0   | 1   | 0 to 15        | 00000000h-000FFFFFh | 1MB     | Lower 1/128  |

| 1                       | 0   | 1   | 1   | 0   | 0 to 31        | 00000000h-001FFFFFh | 2MB     | Lower 1/64   |

| 1                       | 0   | 1   | 1   | 1   | 0 to 63        | 00000000h-003FFFFFh | 4MB     | Lower 1/32   |

| 1                       | 1   | 0   | 0   | 0   | 0 to 127       | 00000000h-007FFFFFh | 8MB     | Lower 1/16   |

| 1                       | 1   | 0   | 0   | 1   | 0 to 255       | 00000000h-00FFFFFFh | 16MB    | Lower 1/8    |

| 1                       | 1   | 0   | 1   | 0   | 0 to 511       | 00000000h-01FFFFFFh | 32MB    | Lower 1/4    |

| 1                       | 1   | 0   | 1   | 1   | 0 to 1023      | 00000000h-03FFFFFFh | 64MB    | Lower 1/2    |

| X                       | 1   | 1   | X   | X   | ALL            | 00000000h-07FFFFFFh | 128MB   | ALL          |

**Table 5. GD55B01GF Protected area size (CMP=1)**

| Status Register Content |     |     |     |     | Memory Content |                      |           |                 |

|-------------------------|-----|-----|-----|-----|----------------|----------------------|-----------|-----------------|

| BP4                     | BP3 | BP2 | BP1 | BP0 | Blocks         | Addresses            | Density   | Portion         |

| X                       | 0   | 0   | 0   | 0   | ALL            | 00000000H-07FFFFFFH  | 128MB     | ALL             |

| 0                       | 0   | 0   | 0   | 1   | 0 to 2046      | 00000000H-07FEFFFFH  | 131,008KB | Lower 2047/2048 |

| 0                       | 0   | 0   | 1   | 0   | 0 to 2045      | 00000000H-07FDFFFFH  | 130,944KB | Lower 1023/1024 |

| 0                       | 0   | 0   | 1   | 1   | 0 to 2043      | 00000000H-07FBFFFFH  | 130,816KB | Lower 511/512   |

| 0                       | 0   | 1   | 0   | 0   | 0 to 2039      | 00000000H-07F7FFFFH  | 130,560KB | Lower 255/256   |

| 0                       | 0   | 1   | 0   | 1   | 0 to 2031      | 00000000H-07EFFFFFH  | 127MB     | Lower 127/128   |

| 0                       | 0   | 1   | 1   | 0   | 0 to 2015      | 00000000H-07DFFFFFH  | 126MB     | Lower 63/64     |

| 0                       | 0   | 1   | 1   | 1   | 0 to 1983      | 00000000H-07BFFFFFH  | 124MB     | Lower 31/32     |

| 0                       | 1   | 0   | 0   | 0   | 0 to 1919      | 00000000H-077FFFFFFH | 120MB     | Lower 15/16     |

| 0                       | 1   | 0   | 0   | 1   | 0 to 1791      | 00000000H-06FFFFFFH  | 112MB     | Lower 7/8       |

| 0                       | 1   | 0   | 1   | 0   | 0 to 1535      | 00000000H-05FFFFFFH  | 96MB      | Lower 3/4       |

| 0                       | 1   | 0   | 1   | 1   | 0 to 1023      | 00000000H-03FFFFFFH  | 64MB      | Lower 1/2       |

| 1                       | 0   | 0   | 0   | 1   | 1 to 2047      | 00010000H-07FFFFFFH  | 131,008KB | Upper 2047/2048 |

| 1                       | 0   | 0   | 1   | 0   | 2 to 2047      | 00020000H-07FFFFFFH  | 130,944KB | Upper 1023/1024 |

| 1                       | 0   | 0   | 1   | 1   | 4 to 2047      | 00040000H-07FFFFFFH  | 130,816KB | Upper 511/512   |

| 1                       | 0   | 1   | 0   | 0   | 8 to 2047      | 00080000H-07FFFFFFH  | 130,560KB | Upper 255/256   |

| 1                       | 0   | 1   | 0   | 1   | 16 to 2047     | 00100000H-07FFFFFFH  | 127MB     | Upper 127/128   |

| 1                       | 0   | 1   | 1   | 0   | 32 to 2047     | 00200000H-07FFFFFFH  | 126MB     | Upper 63/64     |

| 1                       | 0   | 1   | 1   | 1   | 64 to 2047     | 00400000H-07FFFFFFH  | 124MB     | Upper 31/32     |

| 1                       | 1   | 0   | 0   | 0   | 128 to 2047    | 00800000H-07FFFFFFH  | 120MB     | Upper 15/16     |

| 1                       | 1   | 0   | 0   | 1   | 256 to 2047    | 01000000H-07FFFFFFH  | 112MB     | Upper 7/8       |

| 1                       | 1   | 0   | 1   | 0   | 512 to 2047    | 02000000H-07FFFFFFH  | 96MB      | Upper 3/4       |

| 1                       | 1   | 0   | 1   | 1   | 1024 to 2047   | 04000000H-07FFFFFFH  | 64MB      | Upper 1/2       |

| X                       | 1   | 1   | X   | X   | NONE           | NONE                 | NONE      | NONE            |

### **Volatile Lock (VL) Registers**

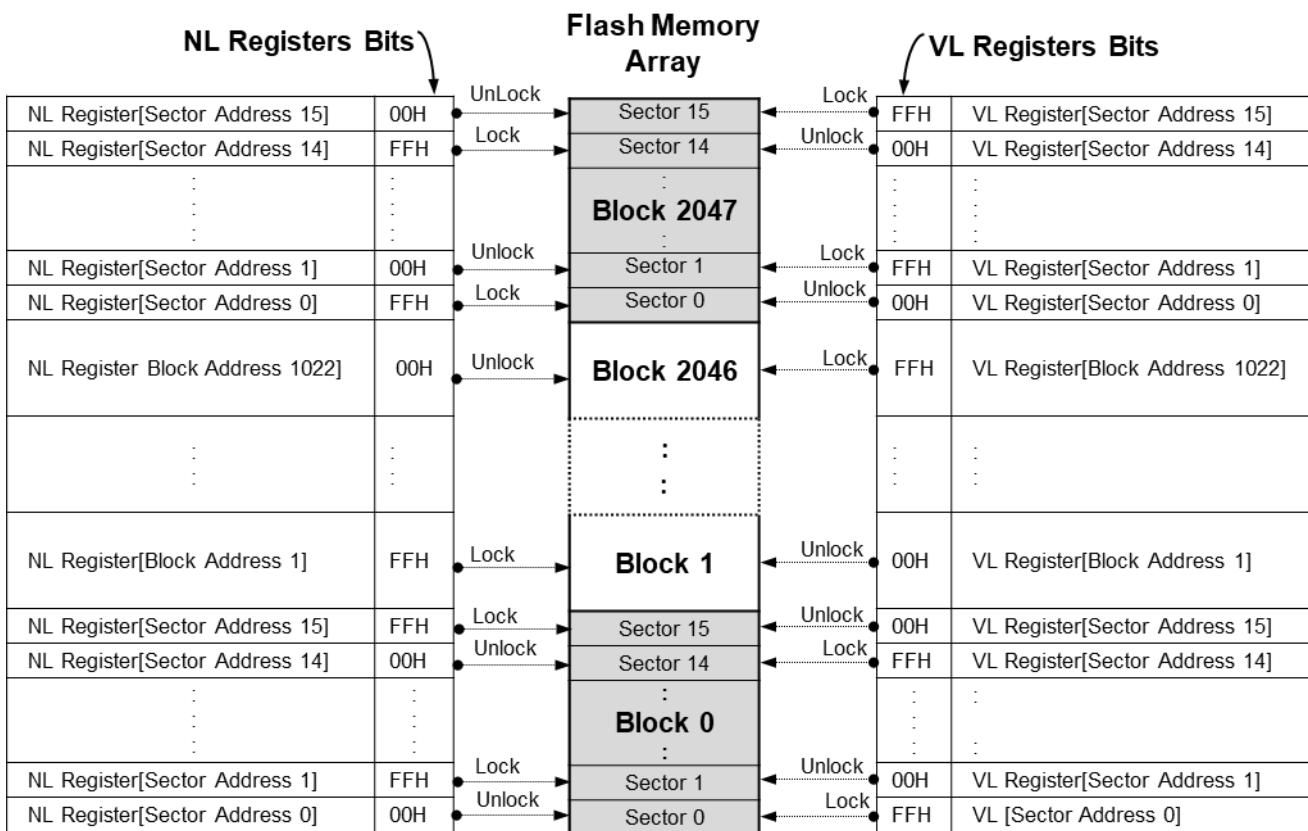

The GD55B01GF has a total of 2078 Volatile Lock Registers. Each VL Register has 8-bits. The VL Register is read independently by Read VL Register (E0H) using either a sector or block address. Each VL Register is written independently by Write VL Register (E1H) instruction using either a sector or block address. All VL Registers are cleared collectively by Global VL Registers Unlock (98H) instruction and set collectively by Global VL Registers Lock (7EH) instruction.

The bottom and top 64KB Blocks have individual volatile protection lock registers on each 4KB sectors (total 32). The middle 64KB Blocks have their own individual volatile block lock registers (total 2046). The VL register mapping assignments to the memory sectors/blocks are illustrated on Figure 6. The default value of the VL Registers from power up or reset is based on the VL Default value (NVCR Address <02> Bit 2). VL Register value of '00H' indicates the corresponding sectors or blocks are unprotected. A VL Register value of 'FFH' indicates the corresponding sectors or blocks are protected.

| No.                                                                 | Name         | Description                                                                                                                                                                        | Note                 |

|---------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2078 VL Registers[Sector/Block Address] = 00h or FFh <sup>(1)</sup> | VL Registers | Each VL Register protects or unprotect a corresponding sector or block:<br>00H = Unprotected Sector/Block<br>FFH = Protected Sector/Block<br>Others = Not Supported <sup>(2)</sup> | Volatile<br>Writable |

Notes:

1. VL Registers mapping across the full memory is illustrated on Figure 6 (NL and VL Registers Assignment on the Memory). Default value of the VL Registers from power up or reset is based on VL Default value set on NVCR Address <02> Bit 2.

2. Only valid data (00H or FFH) are valid and accepted during Write VL Register. Other data combinations are not valid data input; the Write VL Register command will be ignored; and the WEL bit will not be cleared.

### **Nonvolatile Lock (NL) Registers**

The GD55B01GF has a total of 2078 Nonvolatile Lock Registers that are non-volatile. Each NL Register has 8-bits. The NL Register is read independently using either a sector or block address using Read NL Register (E2H) instruction. Each NL Register is also set independently by Set NL Register (E3H) instruction using either a sector or block address. All NL Registers are cleared collectively by Clear All NL Registers (E4H) instruction.

The bottom and top 64KB Blocks have individual non-volatile protection lock registers on each 4KB sectors (total 32). The middle 64KB Blocks have their own individual non-volatile block lock registers (total 2046). The NL Register mapping assignments to the memory sectors/blocks are illustrated on Figure 6. The factory default value of the NL Registers is '00H' indicating the corresponding sectors or blocks are unprotected. When NL Register is set to 'FFH', the corresponding sector or block is protected against program or erase.

| No.                                                                 | Name         | Description                                                                                                                                                         | Note                  |

|---------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 2078 NL Registers[Sector/Block Address] = 00h or FFh <sup>(1)</sup> | NL Registers | Each NL Register protects or unprotect a corresponding sector or block:<br>00H = Unprotected Sector/Block<br>FFH = Protected Sector/Block<br>Others = Not Supported | Non-Volatile Writable |

Note:

1. NL Registers mapping across the full memory is illustrated on Figure 6 (NL and VL Registers Assignment on the Memory).

**Figure 6. NL Registers and VL Registers Assignment on the Memory**

Notes:

1. The first and last blocks will have NL/VL Registers protections at the 4KB sector level. Each 4KB sector in these blocks can be individually locked by NL/VL Registers setting.

2. Each of the middle 64KB blocks has NL/VL Registers protections at the 64KB block level. Each 64KB block can be individually locked by NL/VL Registers setting.

## 6 REGISTERS

### 6.1 Status Register

Table 6. Status Register-SR No.1

| No. | Bit Name | Description                    | Note                  |

|-----|----------|--------------------------------|-----------------------|

| S7  | SRP0     | Status Register Protection Bit | Non-volatile writable |

| S6  | BP4      | Block Protect Bit              | Non-volatile writable |

| S5  | BP3      | Block Protect Bit              | Non-volatile writable |

| S4  | BP2      | Block Protect Bit              | Non-volatile writable |

| S3  | BP1      | Block Protect Bit              | Non-volatile writable |

| S2  | BP0      | Block Protect Bit              | Non-volatile writable |

| S1  | WEL      | Write Enable Latch             | Volatile, read only   |

| S0  | WIP      | Erase/Write In Progress        | Volatile, read only   |

Table 7. Status Register-SR No.2

| No. | Bit Name | Description                    | Note                        |

|-----|----------|--------------------------------|-----------------------------|

| S15 | SUS1     | Erase Suspend Bit              | Volatile, read only         |

| S14 | SRP1     | Status Register Protection Bit | Non-volatile writable       |

| S13 | LB3      | Security Register Lock Bit     | Non-volatile writable (OTP) |

| S12 | LB2      | Security Register Lock Bit     | Non-volatile writable (OTP) |

| S11 | LB1      | Security Register Lock Bit     | Non-volatile writable (OTP) |

| S10 | SUS2     | Program Suspend Bit            | Volatile, read only         |

| S9  | QE       | Quad Enable Bit                | QE = 1 permanently          |

| S8  | ADS      | Current Address Mode Bit       | Volatile, read only         |

Table 8. Status Register-SR No.3

| No. | Bit Name | Description               | Note                  |

|-----|----------|---------------------------|-----------------------|

| S23 | Reserved | Reserved                  | Reserved              |

| S22 | Reserved | Reserved                  | Reserved              |

| S21 | Reserved | Reserved                  | Reserved              |

| S20 | ADP      | Power Up Address Mode Bit | Non-volatile writable |

| S19 | CMP      | Complement Protect        | Non-volatile writable |

| S18 | Reserved | Reserved                  | Reserved              |

| S17 | DC1      | Dummy Configuration Bit   | Non-volatile writable |

| S16 | DC0      | Dummy Configuration Bit   | Non-volatile writable |

The status and control bits of the Status Register are as follows:

#### **WIP bit**

The Write in Progress (WIP) bit indicates whether the memory is busy in program/erase/write status register or configuration register progress. When WIP bit sets to 1, means the device is busy in program/erase/write status register or configuration register progress, when WIP bit sets 0, means the device is not in program/erase/write status register or configuration register progress.

#### **WEL bit**

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write, Program or Erase command is accepted.

#### **BP4, BP3, BP2, BP1, BP0 bits**

The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase commands. These bits are written with the Write Status Register (WRSR) command. When the Block Protect (BP4, BP3, BP2, BP1, and BP0) bits are set to 1, the relevant memory area becomes protected against Page Program (PP), Sector Erase (SE) and Block Erase (BE) commands. The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits can be written provided that the Hardware Protected mode has not been set. The Chip Erase (CE) command is executed only if none sector or block is protected.

#### **SRP0, SRP1 bits**

The Status Register Protect (SRP1 and SRP0) bits are non-volatile Read/Write bits in the status register. The SRP bits control the method of write protection: software protection, hardware protection, power supply lock-down or one-time programmable protection.

| <b>SRP1</b> | <b>SRP0</b> | <b>#WP</b> | <b>Status Register/NL Register</b>       | <b>Description</b>                                                                                                                                                |

|-------------|-------------|------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | 0           | X          | Software Protected                       | The Status Register and NL Registers can be written to after a Write Enable command, WEL=1. (Default)                                                             |

| 0           | 1           | 0          | Hardware Protected                       | WP#=0, the Status Register and NL Registers are locked and cannot be written to.                                                                                  |

| 0           | 1           | 1          | Hardware Unprotected                     | WP#=1, the Status Register and NL Registers are unlocked and can be written to after a Write Enable command, WEL=1.                                               |

| 1           | 0           | X          | Power Supply Lock-Down <sup>(1)(2)</sup> | Status Register and NL Registers are protected and cannot be written to again until the next Power-Down, Power-Up cycle, Software Reset(66h+99h), Hardware Reset. |

| 1           | 1           | X          | One Time Program <sup>(2)</sup>          | Status Register and NL Registers are permanently protected and cannot be written to.                                                                              |

Notes:

1. When SRP1, SRP0= (1, 0), a Power-Down, Power-Up cycle, Software reset (66H+99H), Hardware Reset will change SRP1, SRP0 to (0, 0) state.

2. This feature is available on special order. Please contact GigaDevice for details.

#### **ADS bit**

The Address Status (ADS) bit is a read only bit that indicates the current address mode the device is operating in. The

device is in 3-Byte address mode when ADS=0 (default), and in 4-Byte address mode when ADS=1.

#### **QE bit**

The Quad Enable (QE) bit is a non-volatile bit in the Status Register that allows Quad operation. The default value of QE bit is 1 and it cannot be changed, the IO2 pin is enabled for Quad SPI, the WP# pin is still available for Standard/Dual SPI.

#### **SUS1, SUS2 bits**

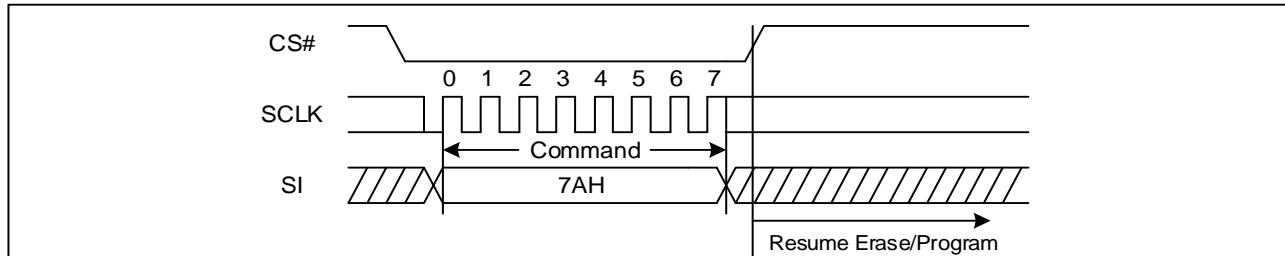

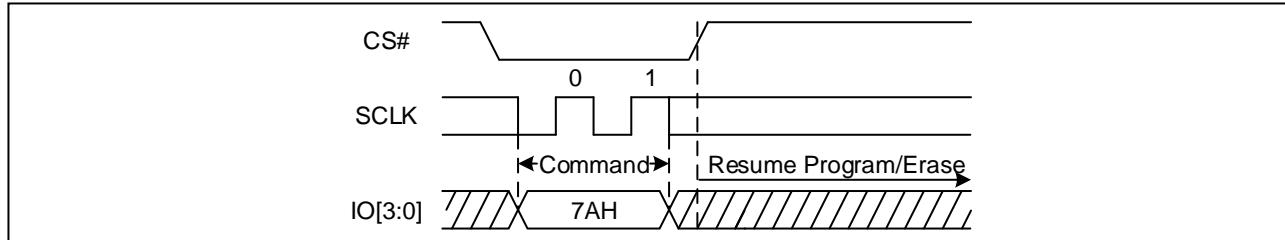

The SUS1 and SUS2 bits are read only bits in the status register (S15 and S10) that are set to 1 after executing an Program/Erase Suspend (75H) command (The Erase Suspend will set the SUS1 bit to 1, and the Program Suspend will set the SUS2 bit to 1). The SUS1 and SUS2 bits are cleared to 0 by Erase/Program Resume (7AH) command, software reset (66H+99H) command as well as a power-down, power-up cycle.

#### **LB3, LB2, LB1 bits**

The LB3, LB2 and LB1 bits are non-volatile One Time Program (OTP) bits in Status Register (S13, S12 and S11) that provide the write protect control and status to the Security Registers. The default state of LB3, LB2 and LB1 bits are 0, the security registers are unlocked. The LB3, LB2 and LB1 bits can be set to 1 individually using the Write Register instruction. The LB3, LB2 and LB1 bits are One Time Programmable, once they are set to 1, the Security Registers will become read-only permanently.

#### **DC1, DC0 bits**

The Dummy Configuration (DC) bits are non-volatile, which select the number of dummy cycles between the end of address and the start of read data output. Dummy cycles provide additional latency that is needed to complete the initial read access of the flash array before data can be returned to the host system. Some read commands require additional dummy cycles as the SCLK frequency increases.

The following dummy cycle tables provide different dummy cycle settings that are configured.

| Command                          | DC1, DC0     | Dummy Cycles | Freq.(MHz) |

|----------------------------------|--------------|--------------|------------|

| 0BH, 0CH<br>3BH, 3CH<br>6BH, 6CH | 00 (default) | 8            | 133        |

|                                  | 01           | 8            | 133        |

|                                  | 10           | 8            | 133        |

|                                  | 11           | 8            | 133        |

| BBH, BCH                         | 00 (default) | 4            | 104        |

|                                  | 01           | 8            | 133        |

|                                  | 10           | 4            | 104        |

|                                  | 11           | 8            | 133        |

| EBH, ECH                         | 00 (default) | 6            | 104        |

|                                  | 01           | 10           | 133        |

|                                  | 10           | 6            | 104        |

|                                  | 11           | 10           | 133        |

#### **CMP bit**

The CMP bit is a non-volatile Read/Write bit in the Status Register (S19). It is used in conjunction with the BP4-BP0 bits to

provide more flexibility for the array protection. Please see the Status registers Memory Protection table for details. The default setting is CMP=0.

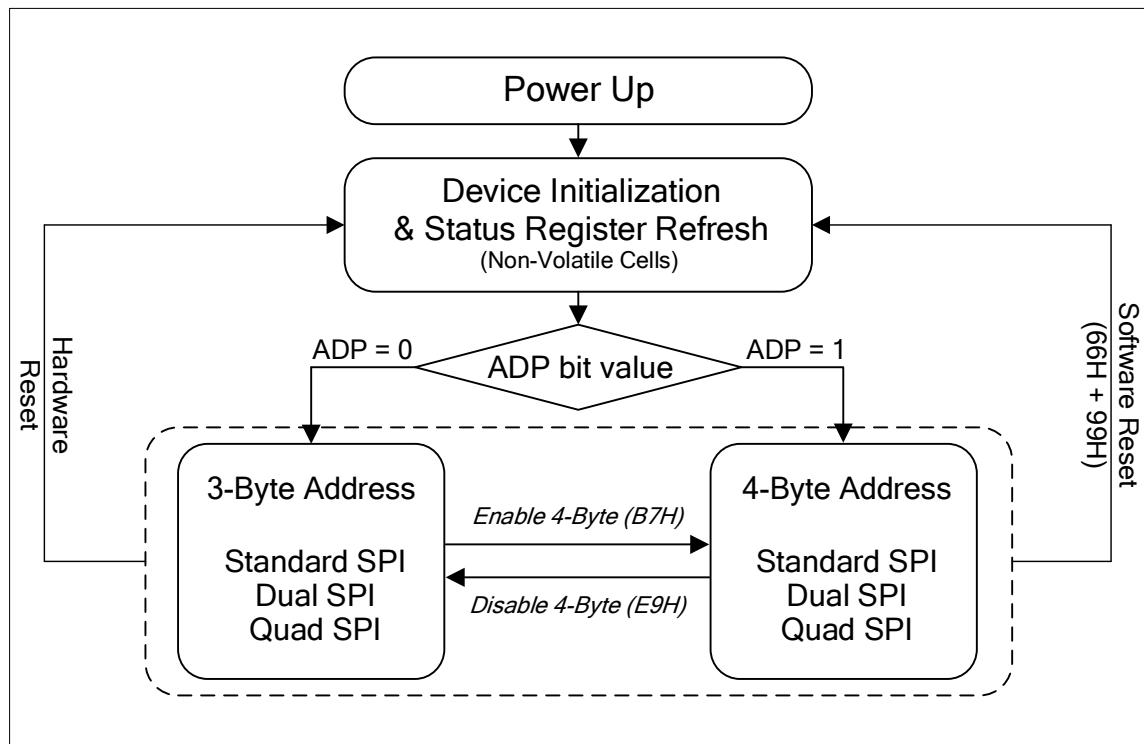

#### ADP bit

The Address Power-up (ADP) bit is a non-volatile writable bit that determines the initial address mode when the device is powered on or reset. This bit is only used during the power on or device reset initialization period. When ADP=0 (factory default), the device will power up into 3-Byte address mode, the Extended Address Register must be used to access memory regions beyond 128Mb. When ADP=1, the device will power up into 4-Byte address mode directly.

## 6.2 Extended Address Register

Table 9 Extended Address Register

| No. | Name     | Description | Note              |

|-----|----------|-------------|-------------------|

| EA7 | Reserved | Reserved    | Reserved          |

| EA6 | Reserved | Reserved    | Reserved          |

| EA5 | Reserved | Reserved    | Reserved          |

| EA4 | Reserved | Reserved    | Reserved          |

| EA3 | Reserved | Reserved    | Reserved          |

| EA2 | A26      | Address bit | Volatile writable |

| EA1 | A25      | Address bit | Volatile writable |

| EA0 | A24      | Address bit | Volatile writable |

The extended address register is only used when the address mode is 3-Byte mode, as to set the higher address. The default value of the address bit is "0".

For the read operation, the whole array can be continually read out with one command. Data output starts from the selected 128Mb, and it can cross the boundary. When the last Byte of the segment is reached, the next Byte (in a continuous reading)

is the first Byte of the next segment. However, the EAR (Extended Address Register) value does not change. The random access reading can only be operated in the selected segment.

The Chip erase command will erase the whole chip and is not limited by EAR selected segment. However, the sector erase, block erase, program operation are limited in selected segment and will not cross the boundary.

#### **A26, A25, A24 bits**

The Extended Address Bits are used only when the device is operating in the 3-Byte Address Mode (ADS=0), which is volatile writable by C5H command.

If the device powers up with ADP bit set to 1, or an “Enter 4-Byte Address Mode (B7H)” instruction is issued, the device will require 4-Byte address input for all address related instructions, and the Extended Address Bit setting will be ignored.

| <b>A26, A25, A24</b> | <b>Address Range</b>  |

|----------------------|-----------------------|

| 000                  | 0000 0000h-00FF FFFFh |

| 001                  | 0100 0000h-01FF FFFFh |

| 010                  | 0200 0000h-02FF FFFFh |

| 011                  | 0300 0000h-03FF FFFFh |

| 100                  | 0400 0000h-04FF FFFFh |

| 101                  | 0500 0000h-05FF FFFFh |

| 110                  | 0600 0000h-06FF FFFFh |

| 111                  | 0700 0000h-07FF FFFFh |

### **6.3 Flag Status Register**

**Table 10 Flag Status Register**

| <b>No.</b> | <b>Name</b> | <b>Description</b> | <b>Note</b>         |

|------------|-------------|--------------------|---------------------|

| FS7        | RY/BY#      | Ready/Busy# Bit    | Volatile, read only |

| FS6        | Reserved    | Reserved           | Reserved            |

| FS5        | Reserved    | Reserved           | Reserved            |

| FS4        | Reserved    | Reserved           | Reserved            |

| FS3        | Reserved    | Reserved           | Reserved            |

| FS2        | Reserved    | Reserved           | Reserved            |

| FS1        | PE          | Program Error Bit  | Volatile, read only |

| FS0        | EE          | Erase Error bit    | Volatile, read only |

The status and control bits of the Flag Status Register are as follows:

#### **RY/BY# bit**

The RY/BY# bit is a read only bit that indicates Program or Erase Status bit. Indicates whether one of the following command cycles is in progress: WRITE STATUS REGISTER, WRITE NONVOLATILE CONFIGURATION REGISTER, PROGRAM, or ERASE.

#### **PE bit**

The Program Error (PE) bit is a read only bit that indicates a program failure. It will also be set when the user attempts to program a protected array sector or access the locked OTP space. PE is cleared to "0" after program operation resumes or

---

by Clear Flag Status Register command (30H).

**EE bit**

The Erase Error (EE) bit is a read only bit that indicates an erase failure. It will also be set when the user attempts to erase a protected array sector or access the locked OTP space. EE is cleared to "0" after erase operation resumes or by Clear Flag Status Register command (30H).

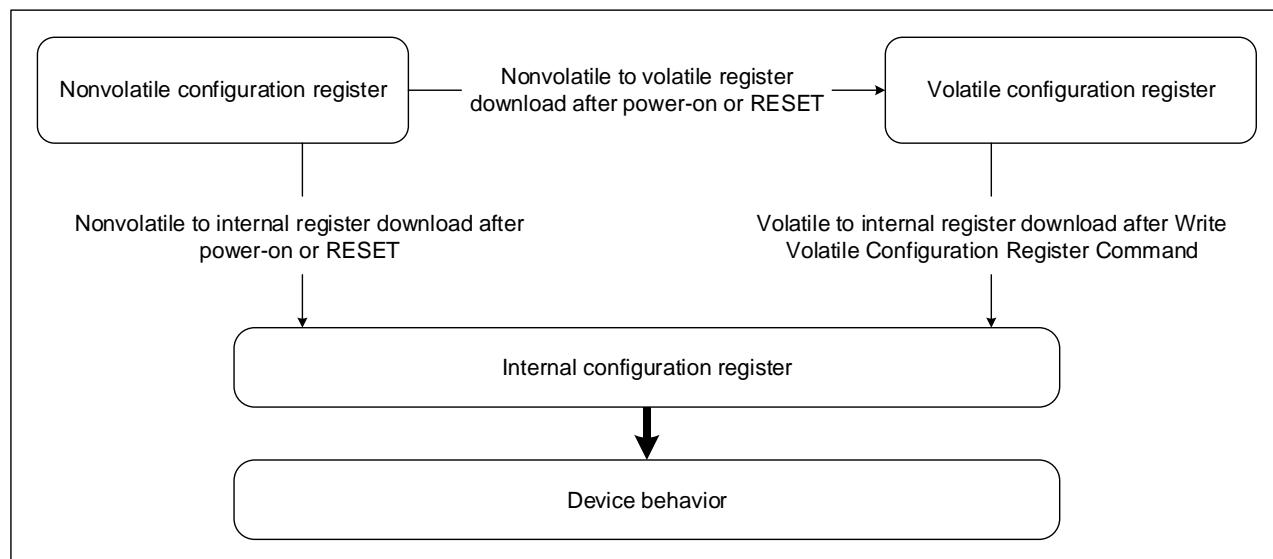

## 7 INTERNAL CONFIGURATION REGISTER

The memory configuration is set by an internal configuration register that is not directly accessible to users. The user can change the default configuration at power up by using the WRITE NONVOLATILE CONFIGURATION REGISTER. Information from the nonvolatile configuration register overwrites the internal configuration register during power on or after a reset.

The user can change the configuration during device operation using the WRITE VOLATILE CONFIGURATION REGISTER command. Information from the volatile configuration registers overwrite the internal configuration register immediately after the WRITE command completes.

### 7.1 Nonvolatile Configuration Register

Nonvolatile Configuration Register bits set the device configuration after power-up or reset. All bits are erased (FFh) unless stated otherwise. This register is read from and written to using the READ NONVOLATILE CONFIGURATION REGISTER and the WRITE NONVOLATILE CONFIGURATION REGISTER commands, respectively. The commands use the main array address scheme, but only the LSB is used to access different register settings, thereby providing up to 256 Bytes of registers (See the table below for the details). A WRITE command to a reserved address will set the device to the default status of the corresponding Byte.

Table 11 Nonvolatile Configuration Register

| Addr | Settings                      | bit7   | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Description                           |

|------|-------------------------------|--------|------|------|------|------|------|------|------|---------------------------------------|

| <0>  | XIP mode after Power on reset | 1      | 1    | 1    | 1    | 1    | 1    | 0    | 0    | XIP: Dual I/O fast read               |

|      |                               | 1      | 1    | 1    | 1    | 1    | 1    | 1    | 0    | XIP: Quad I/O fast read               |

|      |                               | 1      | 1    | 1    | 1    | 1    | 1    | 1    | 1    | Disabled (Default)                    |

|      |                               | Others |      |      |      |      |      |      |      |                                       |

| <1>  | Driver Strength configuration | x      | x    | x    | x    | x    | x    | 0    | 0    | 100%(18 Ohm)                          |

|      |                               | x      | x    | x    | x    | x    | x    | 0    | 1    | 75%(25 Ohm) (default)                 |

|      |                               | x      | x    | x    | x    | x    | x    | 1    | 0    | 50%(35 Ohm)                           |

|      |                               | x      | x    | x    | x    | x    | x    | 1    | 1    | 25%(50 Ohm)                           |

|      |                               | Others |      |      |      |      |      |      |      |                                       |

| <2>  | VL default value              | x      | x    | x    | x    | x    | 1    | x    | x    | all VL=1 after POR or Reset           |

|      |                               | x      | x    | x    | x    | x    | 0    | x    | x    | all VL=0 after POR or Reset (Default) |

|      |                               | Others |      |      |      |      |      |      |      |                                       |

| <3>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <4>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <5>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <6>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <7>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <8>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <9>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <A>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

| <B>  | Reserved                      |        |      |      |      |      |      |      |      |                                       |

## 7.2 Volatile Configuration Register

Volatile Configuration Register bits temporarily set the device configuration after power-up or reset. All bits are erased (FFh) unless stated otherwise. This register is read from and written to using the READ VOLATILE CONFIGURATION REGISTER and the WRITE VOLATILE CONFIGURATION REGISTER commands, respectively. The commands use the main array address scheme; however, only the LSB is used to access different register settings to provide up to 256 Bytes of registers (See the table below for the details). A WRITE command to a reserved address will set the device to the default status of the corresponding Byte.

Table 12 Volatile Configuration Register

| Addr | Settings                        | bit7   | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Description                           |

|------|---------------------------------|--------|------|------|------|------|------|------|------|---------------------------------------|

| <0>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <1>  | Driver Strength configuration   | x      | x    | x    | x    | x    | x    | 0    | 0    | 100%(18 Ohm)                          |

|      |                                 | x      | x    | x    | x    | x    | x    | 0    | 1    | 75%(25 Ohm) (default)                 |

|      |                                 | x      | x    | x    | x    | x    | x    | 1    | 0    | 50%(35 Ohm)                           |

|      |                                 | x      | x    | x    | x    | x    | x    | 1    | 1    | 25%(50 Ohm)                           |

|      |                                 | Others |      |      |      |      |      |      |      | Reserved                              |

| <2>  | VL default value <sup>(1)</sup> | x      | x    | x    | x    | x    | 1    | x    | x    | all VL=1 after POR or Reset           |

|      |                                 | x      | x    | x    | x    | x    | 0    | x    | x    | all VL=0 after POR or Reset (Default) |

|      |                                 | Others |      |      |      |      |      |      |      | Reserved                              |

| <3>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <4>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <5>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <6>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <7>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <8>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <9>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <A>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

| <B>  | Reserved                        |        |      |      |      |      |      |      |      |                                       |

Note:

1. Volatile Configuration Register's VL default value download from Nonvolatile Configuration register after power-on or RESET; Write Volatile Configuration Register (81h) can change Volatile Configuration Register VL default value, but it is invalid;

## 8 COMMAND DESCRIPTIONS

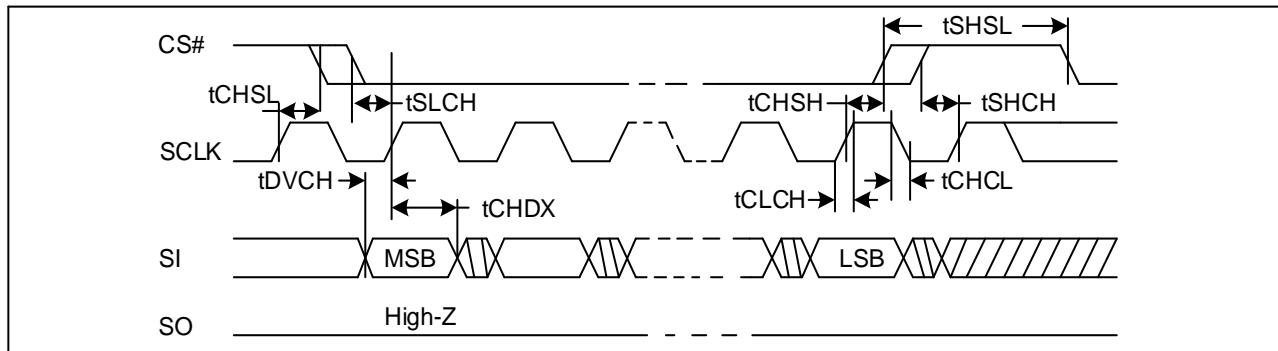

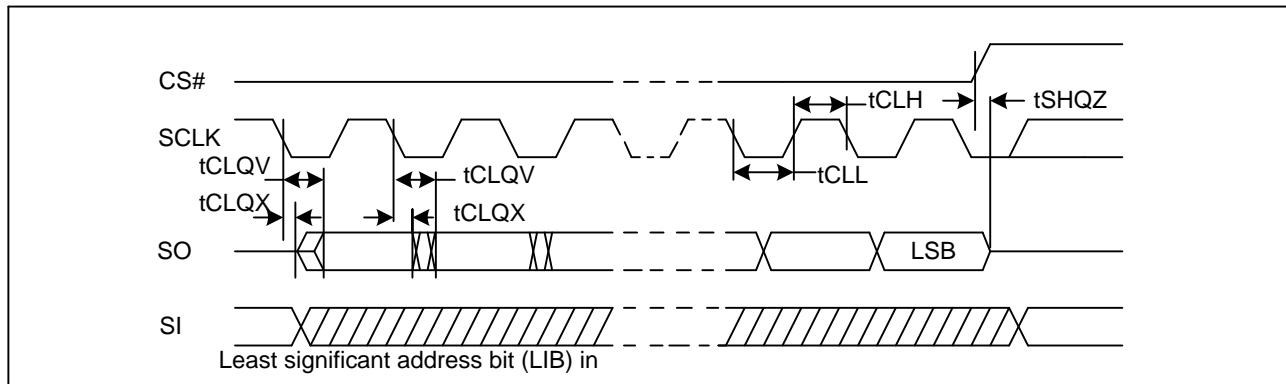

All commands, addresses and data are shifted in and out of the device, beginning with the most significant bit on the first rising edge of SCLK after CS# is driven low. Then, the one-Byte command code must be shifted in to the device, with most significant bit first on SI, and each bit is latched on the rising edges of SCLK.

Every command sequence starts with a one-Byte command code. Depending on the command, this might be followed by address Bytes, or by data Bytes, or by both or none. CS# must be driven high after the last bit of the command sequence has been completed. For the command of Read, Fast Read, Read Status Register or Release from Deep Power-Down, and Read Device ID, the shifted-in command sequence is followed by a data-out sequence. All read instruction can be completed after any bit of the data-out sequence is being shifted out, and then CS# must be driven high to return to deselected status.

For the command of Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register, Write Enable, Write Disable or Deep Power-Down command, CS# must be driven high exactly at a Byte boundary, otherwise the command is rejected, and is not executed. That is CS# must be driven high when the number of clock pulses after CS# being driven low is an exact multiple of eight. For Page Program, if at any time the input Byte is not a full Byte, nothing will happen and WEL will not be reset.

**Table 13. Commands (SPI, 3- or 4-Byte Addr. Mode)**

| Command Name                  | Byte 1 | Byte 2    | Byte 3  | Byte 4 | Byte 5 | Byte 6 | Byte 7 | Byte 8 | Byte 9 |

|-------------------------------|--------|-----------|---------|--------|--------|--------|--------|--------|--------|

| Write Enable                  | 06H    |           |         |        |        |        |        |        |        |

| Write Disable                 | 04H    |           |         |        |        |        |        |        |        |

| Read Status Register-1        | 05H    | (S7-S0)   | (cont.) |        |        |        |        |        |        |

| Read Status Register-2        | 35H    | (S15-S8)  | (cont.) |        |        |        |        |        |        |

| Read Status Register-3        | 15H    | (S23-S16) | (cont.) |        |        |        |        |        |        |

| Read Flag Status Register     | 70H    | FS7~FS0   | (cont.) |        |        |        |        |        |        |

| Write Status Register-1       | 01H    | S7-S0     |         |        |        |        |        |        |        |

| Write Status Register-1&2     | 01h    | S7-S0     | S15-S8  |        |        |        |        |        |        |

| Write Status Register-2       | 31H    | S15-S8    |         |        |        |        |        |        |        |

| Write Status Register-3       | 11H    | S23-S16   |         |        |        |        |        |        |        |

| Read Extended Addr. Register  | C8H    | (EA7-EA0) |         |        |        |        |        |        |        |

| Write Extended Addr. Register | C5H    | EA7-EA0   |         |        |        |        |        |        |        |

| Volatile SR write Enable      | 50H    |           |         |        |        |        |        |        |        |

|                                                 |         |                        |                        |                       |                      |                      |                        |         |  |

|-------------------------------------------------|---------|------------------------|------------------------|-----------------------|----------------------|----------------------|------------------------|---------|--|

| Clear SR Flags                                  | 30H     |                        |                        |                       |                      |                      |                        |         |  |

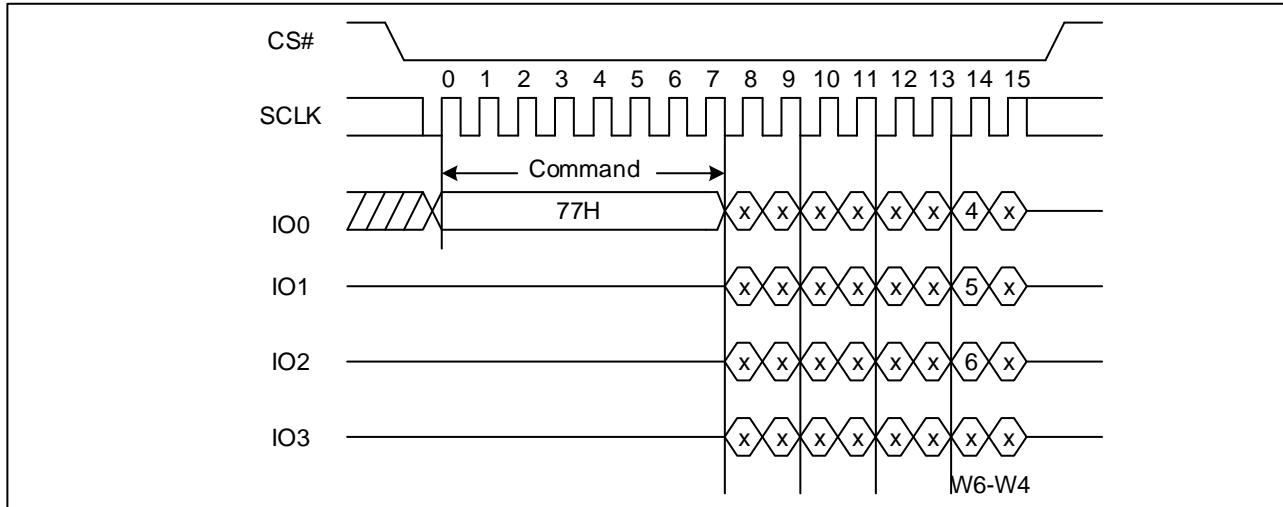

| Set Burst with Wrap                             | 77H     | dummy <sup>(1)</sup>   | dummy <sup>(1)</sup>   | dummy <sup>(1)</sup>  | W7-W0 <sup>(1)</sup> |                      |                        |         |  |

| Chip Erase                                      | 60H/C7H |                        |                        |                       |                      |                      |                        |         |  |

| Enter 4-Byte Address Mode                       | B7H     |                        |                        |                       |                      |                      |                        |         |  |

| Exit 4-Byte Address Mode                        | E9H     |                        |                        |                       |                      |                      |                        |         |  |

| Read Manufacturer/Device ID                     | 90H     | 00H                    | 00H                    | 00H                   | (MID7-MID0)          | (DID7-DID0)          | (cont.)                |         |  |

| Read Identification                             | 9FH     | (M7-M0)                | (JDID15-JDID8)         | (JDID7-JDID0)         | (cont.)              |                      |                        |         |  |

| Enable Reset                                    | 66H     |                        |                        |                       |                      |                      |                        |         |  |

| Reset                                           | 99H     |                        |                        |                       |                      |                      |                        |         |  |

| Program/Erase Suspend                           | 75H     |                        |                        |                       |                      |                      |                        |         |  |

| Program/Erase Resume                            | 7AH     |                        |                        |                       |                      |                      |                        |         |  |

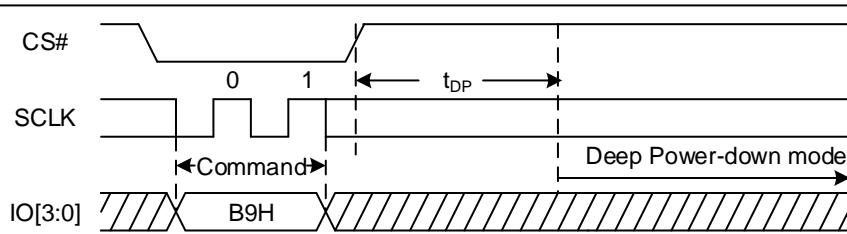

| Deep Power-Down                                 | B9H     |                        |                        |                       |                      |                      |                        |         |  |

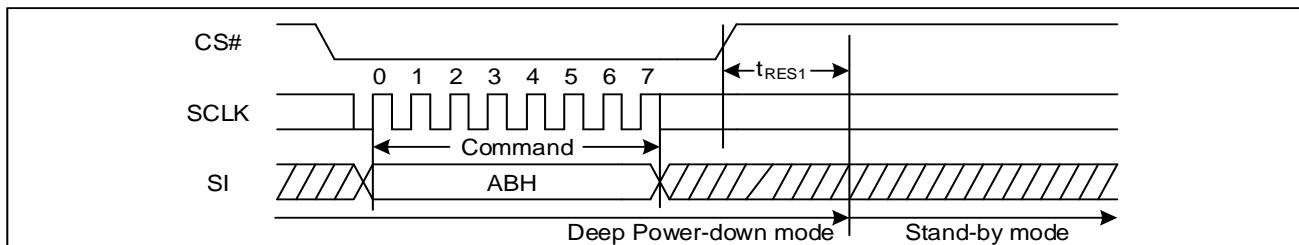

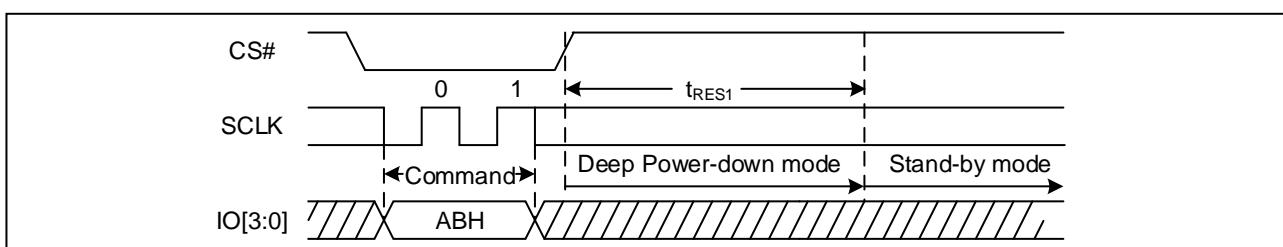

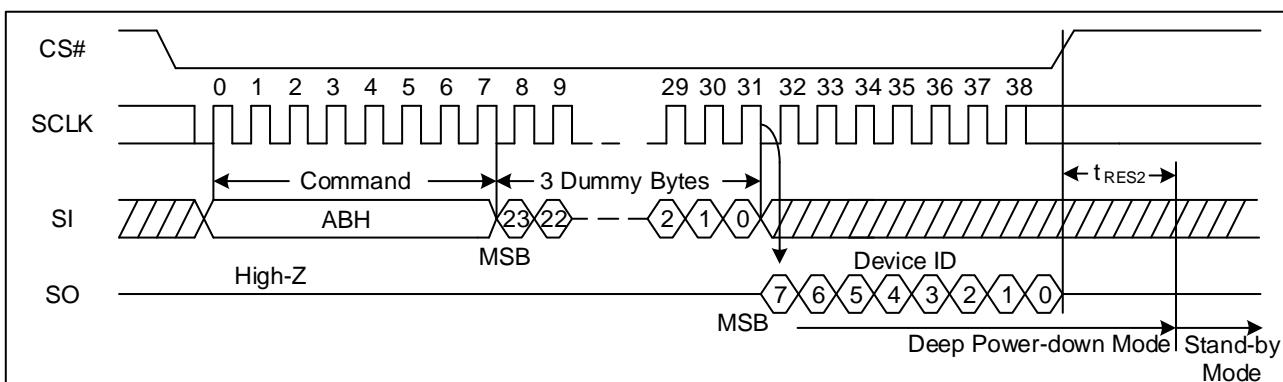

| Release From Deep Power-Down                    | ABH     |                        |                        |                       |                      |                      |                        |         |  |

| Release From Deep Power-Down and Read Device ID | ABH     | dummy                  | dummy                  | dummy                 | (DID7-DID0)          | (cont.)              |                        |         |  |

| Enable QPI                                      | 38H     |                        |                        |                       |                      |                      |                        |         |  |

| Read Serial Flash Discoverable Parameter        | 5AH     | A23-A16                | A15-A8                 | A7-A0                 | dummy                | (D7-D0)              | (cont.)                |         |  |

| Read Data with 4-Byte Address                   | 13H     | A31-A24                | A23-A16                | A15-A8                | A7-A0                | (D7-D0)              | (cont.)                |         |  |

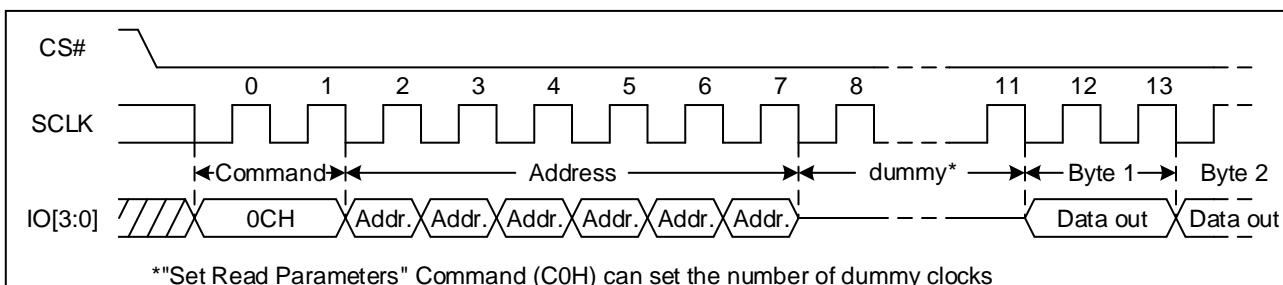

| Fast Read with 4-Byte Address                   | 0CH     | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0)                | (cont.) |  |

| Fast Read Dual Output with 4-Byte Address       | 3CH     | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0) <sup>(2)</sup> | (cont.) |  |

| Fast Read Quad Output with 4-Byte Address       | 6CH     | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0) <sup>(3)</sup> | (cont.) |  |

| Fast Read Dual I/O with 4-Byte Address          | BCH     | A31-A24 <sup>(4)</sup> | A23-A16 <sup>(4)</sup> | A15-A8 <sup>(4)</sup> | A7-A0 <sup>(4)</sup> | M7-M0 <sup>(5)</sup> | (D7-D0) <sup>(2)</sup> | (cont.) |  |

|                                        |     |                        |                        |                       |                      |                      |           |       |                        |

|----------------------------------------|-----|------------------------|------------------------|-----------------------|----------------------|----------------------|-----------|-------|------------------------|

| Fast Read Quad I/O with 4-Byte Address | ECH | A31-A24 <sup>(6)</sup> | A23-A16 <sup>(6)</sup> | A15-A8 <sup>(6)</sup> | A7-A0 <sup>(6)</sup> | M7-M0 <sup>(7)</sup> | dummy     | dummy | (D7-D0) <sup>(3)</sup> |

| Page Program with 4-Byte Address       | 12H | A31-A24                | A23-A16                | A15-A8                | A7-A0                | D7-D0                | Next Byte |       |                        |

| Quad Page Program with 4-Byte Address  | 34H | A31-A24                | A23-A16                | A15-A8                | A7-A0                | D7-D0                | Next Byte |       |                        |

| Sector Erase with 4-Byte Address       | 21H | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |           |       |                        |

| Block Erase (32K) with 4-Byte Address  | 5CH | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |           |       |                        |

| Block Erase (64K) with 4-Byte Address  | DCH | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |           |       |                        |

| Read VL Register                       | E0H | A31-A24                | A23-A16                | A15-A8                | A7-A0                | (D7-D0)              | (cont.)   |       |                        |

| Write VL Register                      | E1H | A31-A24                | A23-A16                | A15-A8                | A7-A0                | D7-D0                |           |       |                        |

| Read NL Register                       | E2H | A31-A24                | A23-A16                | A15-A8                | A7-A0                | (D7-D0)              | (cont.)   |       |                        |

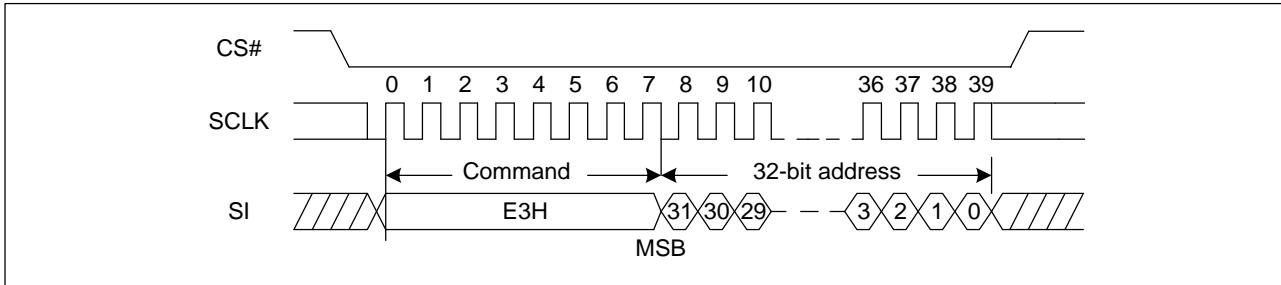

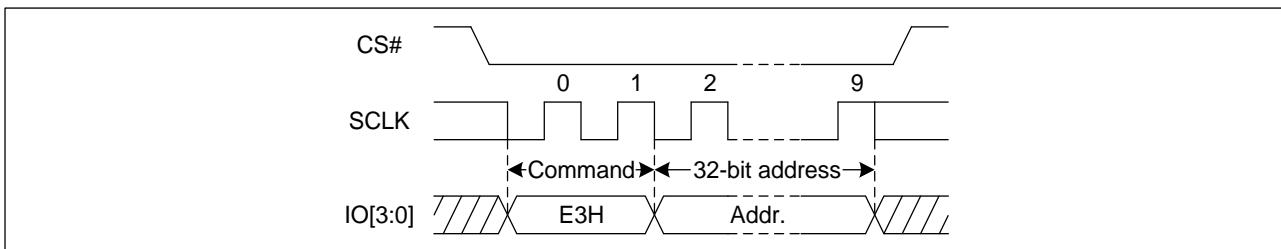

| NL bit Program                         | E3H | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |           |       |                        |

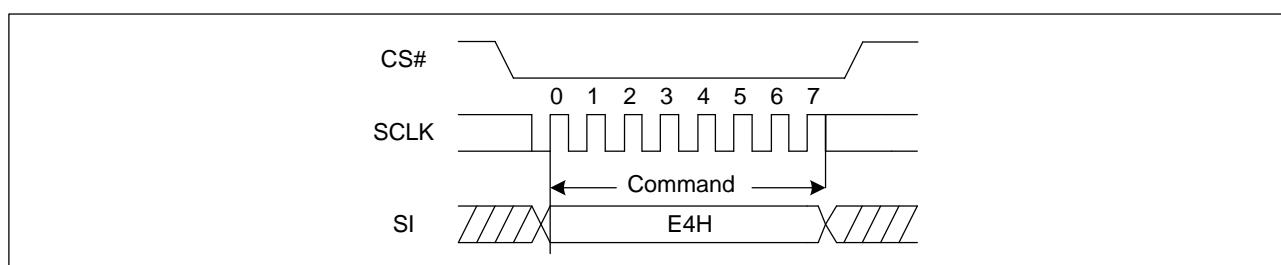

| All NL bit Erase                       | E4H |                        |                        |                       |                      |                      |           |       |                        |

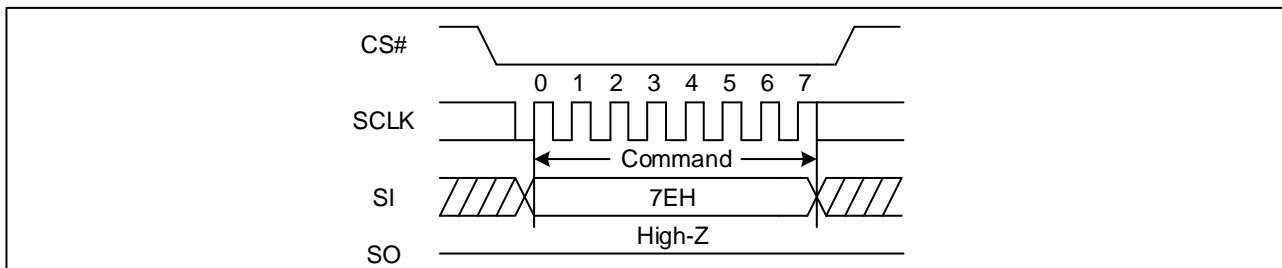

| Global Block Lock                      | 7EH |                        |                        |                       |                      |                      |           |       |                        |

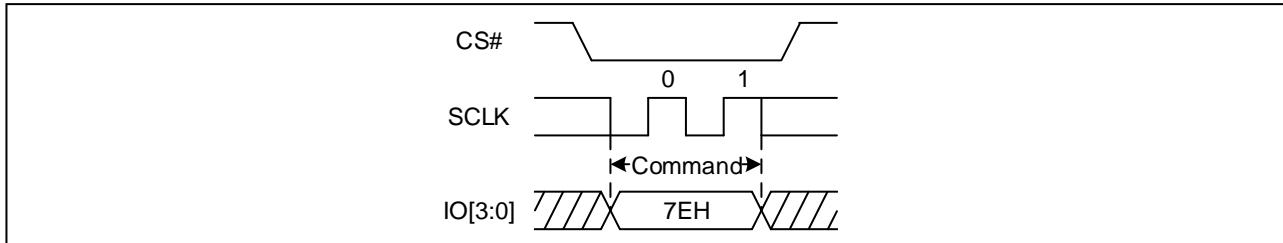

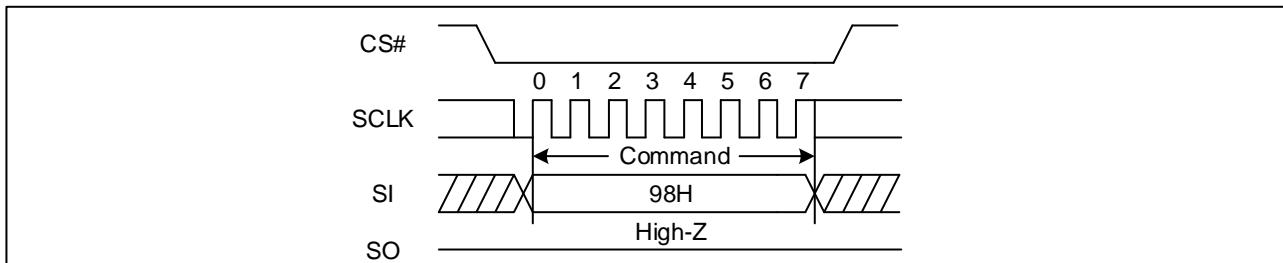

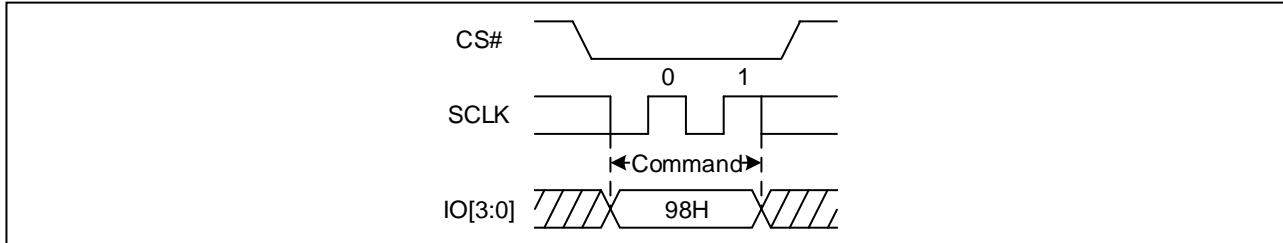

| Global Block Unlock                    | 98H |                        |                        |                       |                      |                      |           |       |                        |

**Table 14. Commands (SPI, 3-Byte Addr. Mode)**

| Command Name          | Byte 1 | Byte 2                  | Byte 3                 | Byte 4                | Byte 5               | Byte 6                 | Byte 7  | Byte 8                 | Byte 9  |

|-----------------------|--------|-------------------------|------------------------|-----------------------|----------------------|------------------------|---------|------------------------|---------|

| Read Data             | 03H    | A23-A16                 | A15-A8                 | A7-A0                 | (D7-D0)              | (cont.)                |         |                        |         |

| Fast Read             | 0BH    | A23-A16                 | A15-A8                 | A7-A0                 | dummy                | (D7-D0)                | (cont.) |                        |         |

| Dual Output Fast Read | 3BH    | A23-A16                 | A15-A8                 | A7-A0                 | dummy                | (D7-D0) <sup>(2)</sup> | (cont.) |                        |         |

| Quad Output Fast Read | 6BH    | A23-A16                 | A15-A8                 | A7-A0                 | dummy                | (D7-D0) <sup>(3)</sup> | (cont.) |                        |         |

| Dual I/O Fast Read    | BBH    | A23-A16 <sup>(9)</sup>  | A15-A8 <sup>(9)</sup>  | A7-A0 <sup>(9)</sup>  | M7-M0 <sup>(5)</sup> | (D7-D0) <sup>(2)</sup> | (cont.) |                        |         |

| Quad I/O Fast Read    | EBH    | A23-A16 <sup>(10)</sup> | A15-A8 <sup>(10)</sup> | A7-A0 <sup>(10)</sup> | M7-M0 <sup>(7)</sup> | dummy                  | dummy   | (D7-D0) <sup>(3)</sup> | (cont.) |

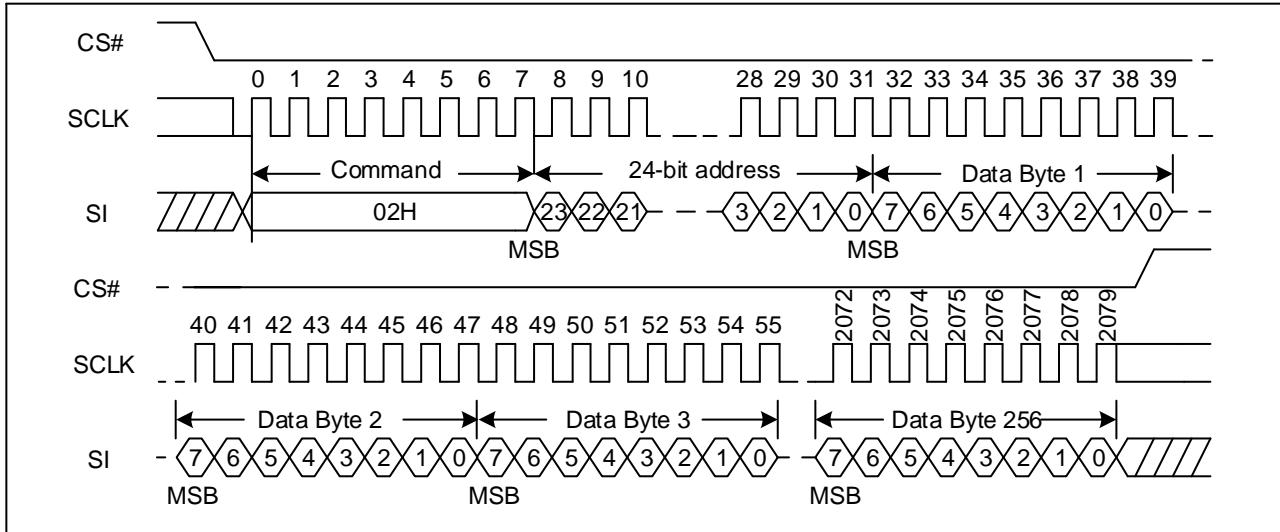

| Page Program          | 02H    | A23-A16                 | A15-A8                 | A7-A0                 | D7-D0                | Next Byte              |         |                        |         |

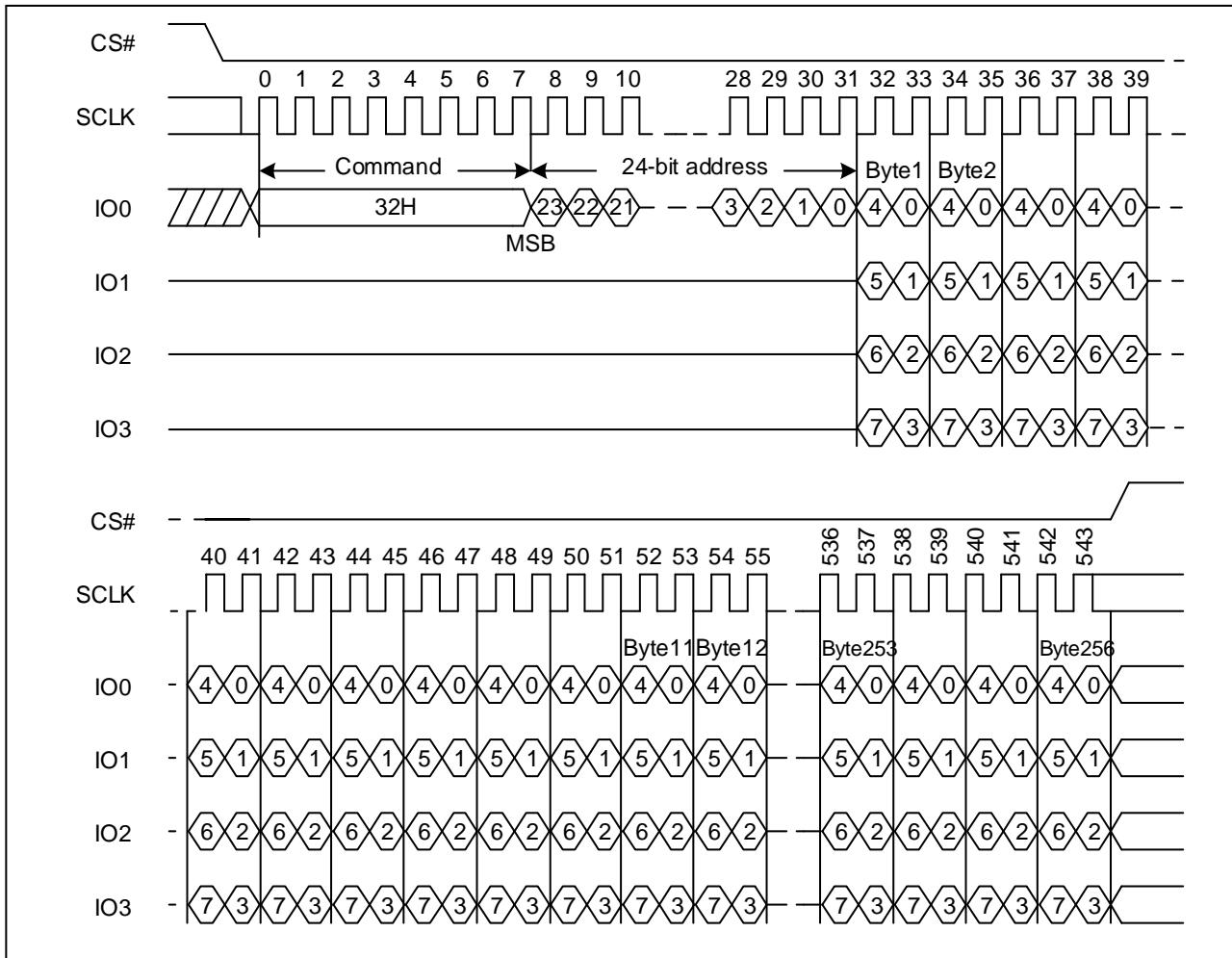

| Quad Page Program     | 32H    | A23-A16                 | A15-A8                 | A7-A0                 | D7-D0                | Next Byte              |         |                        |         |

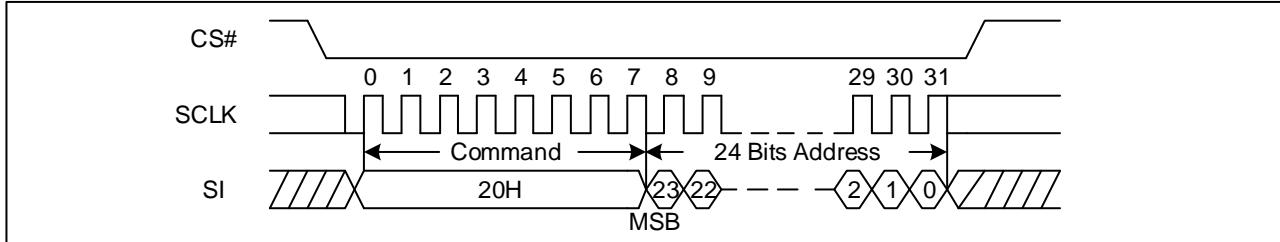

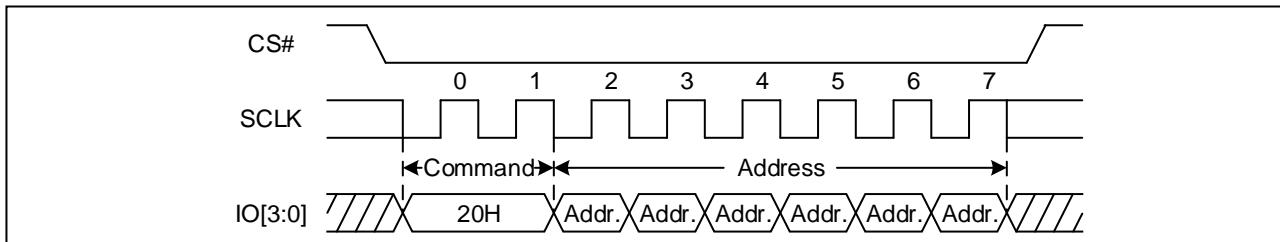

| Sector Erase          | 20H    | A23-A16                 | A15-A8                 | A7-A0                 |                      |                        |         |                        |         |

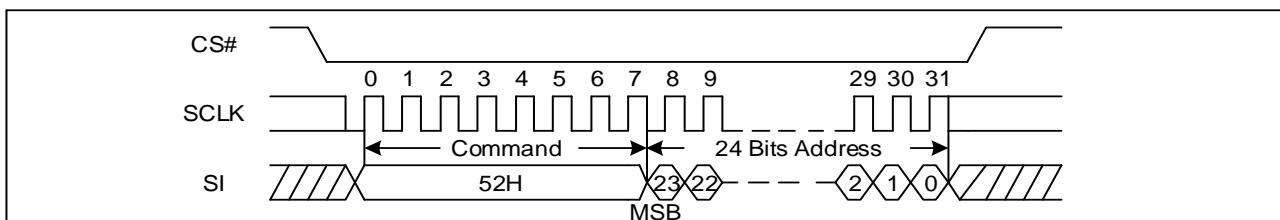

| Block Erase (32K)     | 52H    | A23-A16                 | A15-A8                 | A7-A0                 |                      |                        |         |                        |         |

| Block Erase (64K)     | D8H    | A23-A16                 | A15-A8                 | A7-A0                 |                      |                        |         |                        |         |

|                                               |     |         |        |       |         |                 |         |  |  |

|-----------------------------------------------|-----|---------|--------|-------|---------|-----------------|---------|--|--|

| Read Unique ID                                | 4BH | 00H     | 00H    | 00H   | dummy   | (UID7-<br>UID0) | (cont.) |  |  |

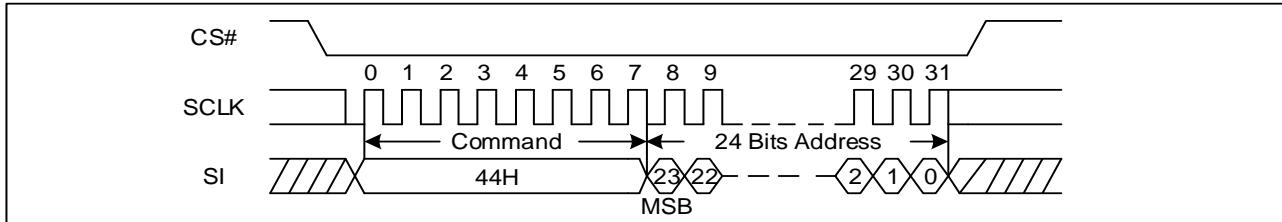

| Erase Security<br>Registers <sup>(11)</sup>   | 44H | A23-A16 | A15-A8 | A7-A0 |         |                 |         |  |  |

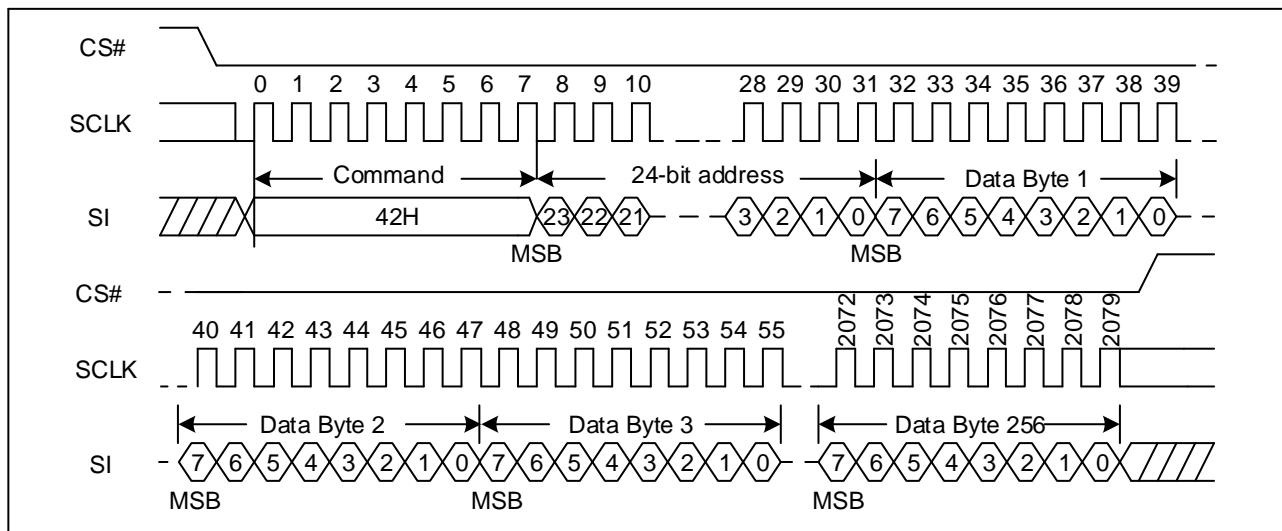

| Program Security<br>Registers <sup>(11)</sup> | 42H | A23-A16 | A15-A8 | A7-A0 | D7-D0   | Next Byte       |         |  |  |

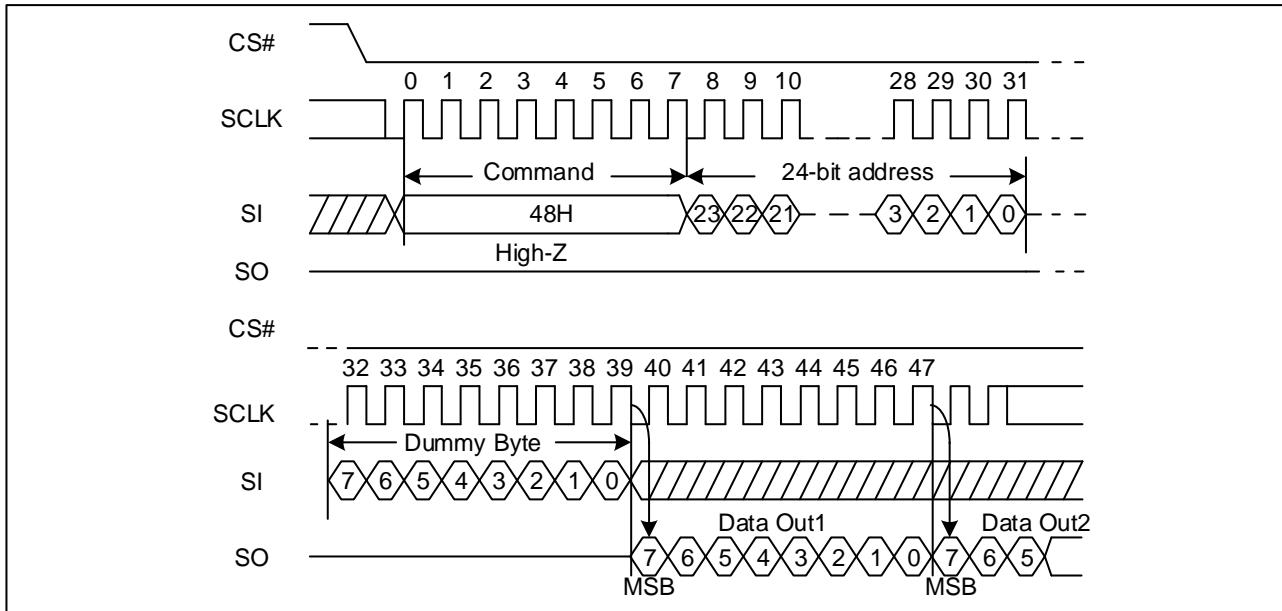

| Read Security<br>Registers <sup>(11)</sup>    | 48H | A23-A16 | A15-A8 | A7-A0 | dummy   | (D7-D0)         | (cont.) |  |  |

| Write Nonvolatile<br>Configuration Register   | B1H | A23-A16 | A15-A8 | A7-A0 | (D7-D0) |                 |         |  |  |

| Write Volatile<br>Configuration Register      | 81H | A23-A16 | A15-A8 | A7-A0 | (D7-D0) |                 |         |  |  |

| Read Nonvolatile<br>Configuration Register    | B5H | A23-A16 | A15-A8 | A7-A0 | dummy   | (D7-D0)         |         |  |  |

| Read Volatile<br>Configuration Register       | 85H | A23-A16 | A15-A8 | A7-A0 | dummy   | (D7-D0)         |         |  |  |

**Table 15. Commands (SPI, 4-Byte Addr. Mode)**

| Command Name                                  | Byte 1 | Byte 2                 | Byte 3                 | Byte 4                | Byte 5               | Byte 6               | Byte 7                 | Byte 8  | Byte 9                     |

|-----------------------------------------------|--------|------------------------|------------------------|-----------------------|----------------------|----------------------|------------------------|---------|----------------------------|

| Read Data                                     | 03H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | (D7-D0)              | (cont.)                |         |                            |

| Fast Read                                     | 0BH    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0)                | (cont.) |                            |

| Dual Output Fast Read                         | 3BH    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0) <sup>(2)</sup> | (cont.) |                            |

| Quad Output Fast<br>Read                      | 6BH    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0) <sup>(3)</sup> | (cont.) |                            |

| Dual I/O Fast Read                            | BBH    | A31-A24 <sup>(4)</sup> | A23-A16 <sup>(4)</sup> | A15-A8 <sup>(4)</sup> | A7-A0 <sup>(4)</sup> | M7-M0 <sup>(5)</sup> | (D7-D0) <sup>(2)</sup> | (cont.) |                            |

| Quad I/O Fast Read                            | EBH    | A31-A24 <sup>(6)</sup> | A23-A16 <sup>(6)</sup> | A15-A8 <sup>(6)</sup> | A7-A0 <sup>(6)</sup> | M7-M0 <sup>(7)</sup> | dummy                  | dummy   | (D7-<br>D0) <sup>(3)</sup> |

| Page Program                                  | 02H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | D7-D0                | Next Byte              |         |                            |

| Quad Page Program                             | 32H    | A31-A24 <sup>(6)</sup> | A23-A16 <sup>(6)</sup> | A15-A8 <sup>(6)</sup> | A7-A0 <sup>(6)</sup> | D7-D0                | Next Byte              |         |                            |

| Sector Erase                                  | 20H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |                        |         |                            |

| Block Erase (32K)                             | 52H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |                        |         |                            |

| Block Erase (64K)                             | D8H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |                        |         |                            |

| Read Unique ID                                | 4BH    | 00H                    | 00H                    | 00H                   | 00H                  | dummy                | (UID7-<br>UID0)        | (cont.) |                            |

| Erase Security<br>Registers <sup>(11)</sup>   | 44H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                |                      |                        |         |                            |

| Program Security<br>Registers <sup>(11)</sup> | 42H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | D7-D0                | Next Byte              |         |                            |

| Read Security<br>Registers <sup>(11)</sup>    | 48H    | A31-A24                | A23-A16                | A15-A8                | A7-A0                | dummy                | (D7-D0)                | (cont.) |                            |

|                                          |     |         |         |        |       |         |         |  |  |

|------------------------------------------|-----|---------|---------|--------|-------|---------|---------|--|--|

| Write Nonvolatile Configuration Register | B1H | A31-A24 | A23-A16 | A15-A8 | A7-A0 | (D7-D0) |         |  |  |

| Write Volatile Configuration Register    | 81H | A31-A24 | A23-A16 | A15-A8 | A7-A0 | (D7-D0) |         |  |  |

| Read Nonvolatile Configuration Register  | B5H | A31-A24 | A23-A16 | A15-A8 | A7-A0 | dummy   | (D7-D0) |  |  |

| Read Volatile Configuration Register     | 85H | A31-A24 | A23-A16 | A15-A8 | A7-A0 | dummy   | (D7-D0) |  |  |

**Table 16. Commands (QPI, 3- or 4-Byte Addr. Mode)**

| Command Name                  | Byte 1  | Byte 2    | Byte 3         | Byte 4        | Byte 5  | Byte 6    | Byte 7  | Byte 8  | Byte 9  |

|-------------------------------|---------|-----------|----------------|---------------|---------|-----------|---------|---------|---------|

| Clock Number                  | (0,1)   | (2,3)     | (4,5)          | (6,7)         | (8,9)   | (10,11)   | (12,13) | (14,15) | (16,17) |